# International Journal of Engineering, Science and Technology Vol. 14, No. 3, 2022, pp. 85-93

INTERNATIONAL JOURNAL OF ENGINEERING, SCIENCE AND TECHNOLOGY

www.ijest1-ng.com www.ajol.info/index.php/ijest © 2022 MultiCraft Limited. All rights reserved

# A seven-level cascaded multilevel inverter based on simplified SVPWM method

Nishant P. Matale<sup>1\*</sup>, Mohan P. Thakre<sup>2</sup>, Payal S. Borse<sup>3</sup>

1\*, 2.3 K.K. Wagh Institute of Engineering Education and Research Nashik, INDIA \*Corresponding Author: e-mail: nishantmatale@gmail.com

#### Abstract

The multilevel converters are extremely widespread alternatives within megawatt power level as well as medium voltage level applications due to their excellent execution than the typical two-level converters. The widely applied control strategies aimed at inverters are Sine Pulse Width Modulation (SPWM) and Space Vector Pulse Width Modulation (SVPWM) strategies. In between these two PWM methods, the SVPWM strategy has excellent execution as compared to the SPWM strategy as a result of improved DC link voltage use as well as a decrease in Total Harmonic Distortion (THD) in output voltages. A traditional SVPWM strategy owns numerous weaknesses like computational complications in terms of identification of the reference voltage vector position, to identify sector, triangle and also it requires large memory for storing look up tables used for switching vectors. This paper presents, an innovative modified SVPWM strategy aimed at Cascaded H-Bridge Multilevel Inverter (CHBMLI). The novel modified SVPWM strategy has overwhelm the downsides of traditional SVPWM strategy. A seven-level CHBMLI is used for the implementation of this simplified SVPWM method to assess performance and as well to made comparison with the SPWM strategy. A MATLAB software is used for the simulation.

Keywords: SVPWM, SPWM, Simplified SVPWM, CHBMLI.

DOI: http://dx.doi.org/10.4314/ijest.v14i3.10S

Cite this article as:

Matale N.P., Thakre M.P., Borse P.S. 2022. A seven-level cascaded multilevel inverter based on simplified svpwm method, *International Journal of Engineering, Science and Technology*, Vol. 14, No. 3, pp. 85-93. doi: 10.4314/ijest.v14i3.10S

Received: January 14, 2022; Accepted: January 14, 2022; Final acceptance in revised form: January 17, 2022

This paper was earlier presented at the SDCEE-2021: 1st International Online Conference on Sustainable Development in Civil and Electrical Engineering, National Institute of Technology Kurukshetra, Kurukshetra, India, December 17-19, 2021 and substantially improved for this Special Issue. Guest Editors: (i) Dr. Sri Niwas Singh, Professor (HAG), Department of Electrical Engineering, Indian Institute of Technology Kanpur, 208016 (U.P.) India, Director, ABV-Indian Institute of Information Technology & Management Gwalior; (ii) Dr. Ashwani Kumar, SMIEEE, Fellow IE (I), Fellow IETE (I), LMISTE, LMSCIEI, Professor and Head, Department of Electrical Engineering, NIT Kurukshetra Haryana, India. Dr. Kumar has 27 years teaching experience and an industrial experience of 2 years, 8 months.

#### 1. Introduction

The necessity of megawatt power and medium voltage level rating equipments within numerous manufacturing processes has been enlarged considerably in the past few years (Rodriguez *et al*, 2009). The large number of motor drives used in various manufacturing processes need megawatt power along with medium voltage level for their satisfactory operation. For such applications, the best option is multilevel inverters (Kouro *et al*, 2010). A staircase waveform of voltage is produced by the multilevel inverter using DC voltage sources and semiconductor switches. The main advantages of multilevel inverters in

comparison with the two-level inverter are drop in harmonics of line voltages and output currents, fewer voltage stress across semiconductor switches, a lesser amount of common mode voltage and improved output wave shape quality (Rodriguez *et al*, 2002). A CHBMLI, Flying-Capacitor (FCMLI) and Diode-Clamped (DCMLI) are the three topologies of multilevel inverter. The CHBMLI is highly popular than other topologies of multilevel inverter due to its merits like extremely integrated construction and less quantity of devices like diodes and capacitors as required in the other two topologies (Rodriguez *et al*, 2007; Maurya *et al*, 2020).

A modulation method plays vital role in the working of all these multilevel inverters. The widely used modulation methods for inverters are SPWM and SVPWM (Attique *et al*, 2017). A SPWM method based on Phase Disposition (PD) is generally used aimed at multilevel inverters because of its merits such as easy execution and lesser computational problem (Sanjay *et al*, 2018). As an alternative, a SVPWM strategy is beneficial as compared to a SPWM strategy owing to improved DC link voltage use, reduced harmonics along with able to operate within over-modulation range (Chowdhary *et al*, 2020; Srivastava *et al*, 2020; Thakre *et al*, 2021; Hu *et al*, 2007; Thakre *et al*, 2020). A conventional SVPWM strategy needs large number of operating stages such as identification of sector number on the basis of reference voltage vector position, finding number of triangles along with its type, calculation of ON periods of dynamic vectors after that the choice of redundant switching conditions, generation of switching order and finally to calculate the ON periods designed for every semiconductor switch (Thakre *et al*, 2020; Manasa *et al*, 2011; Rushiraj *et al*, 2016; Thakre *et al*, 2020).

An implementation of the conventional SVPWM method is comparatively hard due to a large number of triangles plus the large number of surplus switch conditions existing inside the Space Vector Diagram (SVD) (Sabarad *et al*, 2015; Ray *et al*, 2019; Ibrahim *et al*, 2014). In (Prasad *et al*, 2017; Beig *et al*, 2007; Seo *et al*, 2001; Mohamed *et al*, 2009; Ahmed *et al*, 2016), the technique is presented on the basis of disintegrating a three-level SVD into six two-level SVD resulting into large difficulties for higher voltage levels. An additional SVPWM procedure is stated in (Wu et al, 2020; Celanovic *et al*, 2001; Gupta *et al*, 2006) on the basis of 60-degree co-ordinate system has weaknesses such as inappropriate switching conditions and voltage unevenness difficulties within a capacitor. In this paper, an innovative simplified SVPWM strategy aimed at a seven-level CHBMLI is presented. This new simplified SVPWM strategy does not want sector identification, lookup tables and computations as needed within traditional SVPWM strategy.

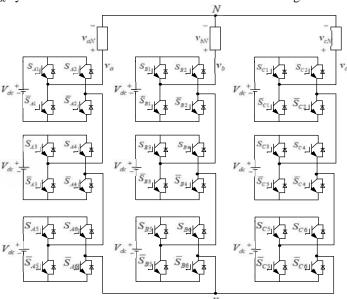

### 2. Cascaded H-Bridge Multilevel Inverter

Figure 1. Seven-level cascaded multilevel inverter

## 3. PWM Techniques

The different modulation strategies are used for multilevel power conversion applications. The two widely used modulation strategies are SPWM and SVPWM strategy. In case of CHBMLI, mostly carrier-based PWM strategies are applied.

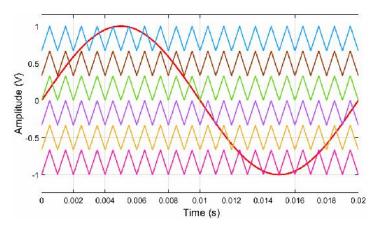

3.1 SPWM Method: There are two key types of carrier-based modulation strategies for the CHBMLI such as level-shifted and phase-shifted PWM. In case of the SPWM strategy, a sine modulating wave is compared with the vertically inclined carrier waves. In order to get seven-level voltage at the output we have to use six triangular carriers as shown in Figure 2. For all these carrier waves the magnitude and frequency are same. The magnitude of inverter output voltage is varied by using Amplitude Modulation Index  $(M_a)$ . For multilevel inverters this  $M_a$  is given by,

$$M_a = \frac{V_m}{V_{cr}(m-1)} \tag{1}$$

Where, V<sub>m</sub> represents modulating wave magnitude and V<sub>cr</sub> represents individual carrier wave magnitude.

Figure 2. Sinusoidal reference wave and triangular carriers for a seven-level CHBMLI

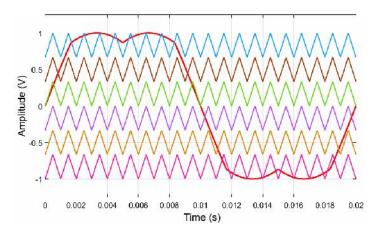

3.2 Simplified SVPWM Method: The traditional SVPWM strategy wants large number of operating stages such as identification of sector number on the basis of reference voltage vector position, identification of triangle number, calculation of ON periods of active vectors after that a choice of redundant switching conditions, generation of switching sequence and finally to calculate the ON periods designed for every switching device. An innovative simplified SVPWM strategy is presented wherein the offset voltage has been included with reference phase voltages. The performance like traditional SVPWM method is obtain when we add this offset voltage with reference phase voltages, we obtain an extreme probable use of DC bus voltage.

$$V_{offset} = -\frac{(V_{\text{max}} + V_{\text{min}})}{2} \tag{2}$$

Where,  $V_{max}$  and  $V_{min}$  are highest and lowest amplitudes of the experimented reference phase voltages in the specific sample period. All dynamic switching vectors of a multilevel converter are gaining positioned in midpoint inside the specified sample interval with the addition of  $V_{offset}$  into the reference phase voltages. Figure 3 illustrated a simplified modulating signal and carrier waves. This modified space vector modulating signals are then compared with carrier waves so as to produce the gate pulses for IGBT switches.

Figure 3. Space vector modulating wave and triangular carriers for a seven-level cascaded multilevel inverter

### 4. Simulation Results

A simulation has been performed in MATLAB software in order to show the usefulness of this new simplified SVPWM strategy. For simulation purpose, the seven-level CHBMLI having RL load is considered. The simulation is carried out for three different values of amplitude modulation index  $(M_a)$ . For these three different values of  $M_a$ , line voltages of the seven-level CHBMLI are attained distinctly for the SPWM and simplified SVPWM strategy together with their harmonic spectrum. The parameters of simulation are stated inside Table 1.

**Table 1**. Parameters of simulation

| Parameter                    | Value   |

|------------------------------|---------|

| DC bus voltage               | 600 V   |

| Switching Frequency          | 1050 Hz |

| Resistive load per phase (R) | 50 ohms |

| Inductive load per phase (L) | 20 mH   |

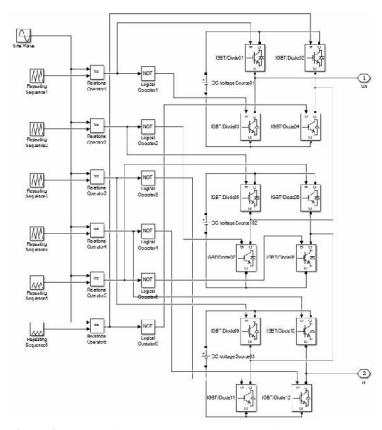

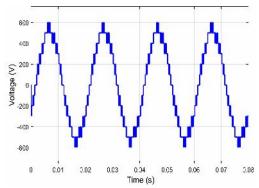

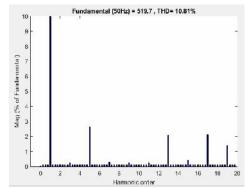

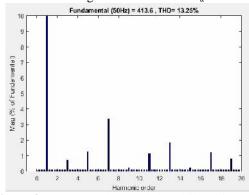

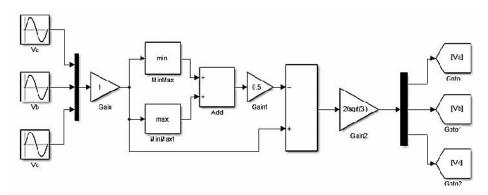

4.1 Simulation results of the seven-level CHBMLI with SPWM strategy: Figure 4 illustrated the scheme of SPWM strategy aimed at a seven-level CHBMLI. Figure 5 shows the seven-level cascaded multilevel inverter line voltage in case of  $M_a$ =1 with a SPWM strategy and Figure 6 illustrated their corresponding harmonic spectrum. Figure 7 illustrated the seven-level cascaded multilevel inverter line voltage in case of  $M_a$ =0.8 with a SPWM strategy. Figure 8 illustrated corresponding harmonic spectrum.

Figure 4. Scheme of the seven-level CHBMLI with SPWM strategy

Figure 5. Seven-level cascaded multilevel inverter line voltage in case of  $M_a$ =1

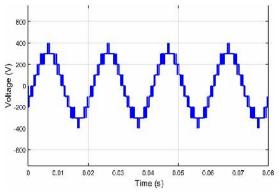

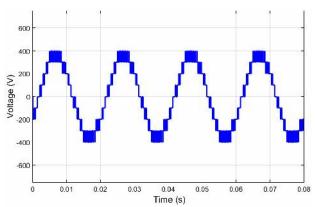

Figure 7. Seven-level cascaded multilevel inverter line voltage in case of M<sub>a</sub>=0.8

Figure 6. Seven-level cascaded multilevel inverter line voltage THD in case of  $M_a$ =1

Figure 8. Seven-level cascaded multilevel inverter line voltage THD in case of  $M_a$ =0.8

Figure 9 illustrated the seven-level cascaded multilevel inverter line voltage in case of M<sub>a</sub>=0.6 with a SPWM strategy. Figure 10 illustrated their corresponding harmonic profile.

**Figure 9.** Seven-level CHBMLI line voltage for  $M_a$ =0.6

Figure 10. Seven-level CHBMLI line voltage THD for  $M_a$ =0.6

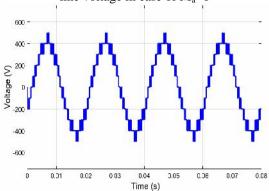

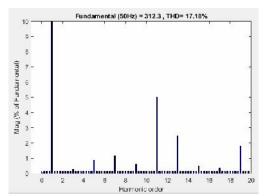

4.2 Simulation results of the seven-level CHBMLI with modified SVPWM strategy: The simulation block in order to generate modified SVPWM reference waves is demonstrated in Figure 11. Figure 12 shows a seven-level cascaded multilevel inverter line voltage in case of  $M_a=1$  with a modified SVPWM strategy. Figure 13 illustrated corresponding harmonic profile.

Figure 11. Simulation block in order to generate modified SVPWM reference waves

Figure 12. Seven-level CHBMLI output line voltage in case of  $M_a$ =1

**Figure 13.** Seven-level cascaded multilevel inverter line voltage THD in case of M<sub>a</sub>=1

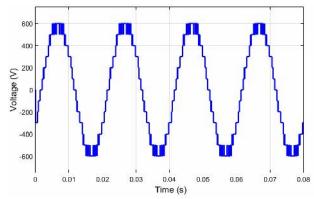

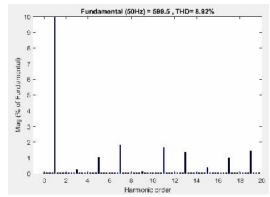

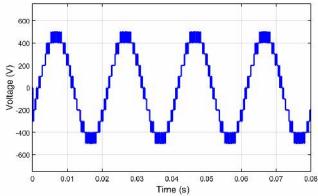

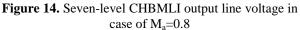

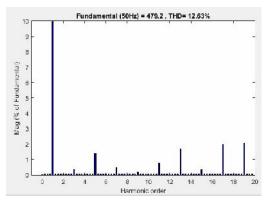

Figure 14 illustrated a seven-level cascaded inverter line voltage in case of  $M_a$ =0.8 with a simplified SVPWM strategy. Figure 15 illustrated their corresponding harmonic profile.

Figure 15. Seven-level CHBMLI line voltage THD for  $M_a$ =0.8

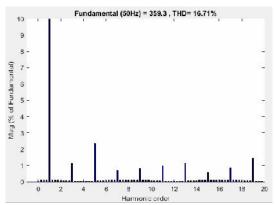

Figure 16 displays a seven-level cascaded inverter line voltage in case of  $M_a$ =0.6 with a simplified SVPWM strategy. Figure 17 illustrated corresponding harmonic profile.

Figure 16. Seven-level CHBMLI output line voltage in case of  $M_a$ =0.6

Figure 17. Seven-level CHBMLI line voltage THD for  $M_a$ =0.6

| Table 2   | Com   | narative | study o | f mo  | dified  | SVI           | PWM | strategy | with     | SPWM strategy   | , |

|-----------|-------|----------|---------|-------|---------|---------------|-----|----------|----------|-----------------|---|

| I unic #. | COIII | puluuve  | bludy 0 | 1 111 | Julilou | $\mathcal{L}$ |     | Bulling  | ** 1 (11 | DI WITT BUILDEY |   |

| Modulation | SPV         | WM          | Simplified SVPWM |             |  |

|------------|-------------|-------------|------------------|-------------|--|

| Index      | THD in      | Fundamental | THD in           | Fundamental |  |

| $(M_a)$    | Line        | Voltage     | Line             | Voltage     |  |

|            | Voltage (%) | Component   | Voltage (%)      | Component   |  |

| 1          | 10.81       | 519.7       | 8.92             | 599.5       |  |

| 0.8        | 13.25       | 413.6       | 12.63            | 479.2       |  |

| 0.6        | 17.18       | 312.3       | 16.71            | 359.3       |  |

When a seven-level cascaded inverter is operated by the modified SVPWM strategy, we obtain higher fundamental voltage component into the line voltages as shown in the simulation results as compared with a SPWM strategy as a result of enhanced DC bus voltage use. As well as, the harmonics are also reduced with a modified SVPWM strategy as compared to the SPWM strategy as stated inside Table 2.

#### 5. Conclusion

In this paper, an innovative modified SVPWM strategy is applied to the seven-level CHBMLI. The new modified SVPWM strategy has disabled the downsides of classical SVPWM strategy as it does not need complicated and tedious calculations to

identify sector, to identify triangle and any look up tables. The comparative study is made among the novel modified SVPWM strategy and SPWM strategy. The simplified SVPWM strategy offers more fundamental voltage component in output line voltage as a result of improved DC bus voltage use than the SPWM strategy. As well as, the harmonics are reduced in seven-level cascaded inverter output line voltage with the modified SVPWM strategy than SPWM strategy. The novel modified SVPWM strategy offers complete benefits as like traditional SVPWM strategy.

#### References

- Ahmed I., Borghate V.B., Matsa A., Meshram P.M., Suryawanshi H.M. and Chaudhari M.A., 2016. Simplified Space Vector Modulation Techniques for Multilevel Inverters. *IEEE Transactions on Power Electronics*, Vol. 31, No. 12, pp. 8483-8499.

- Attique Q.M., Li Y. and Wang K., 2017. A survey on space-vector pulse width modulation for multilevel inverters. *CPSS Transactions on Power Electronics and Applications*, Vol. 2, No. 3, pp. 226-236.

- Beig A.R., Narayanan G. and Ranganathan V.T., 2007. Modified SVPWM Algorithm for Three Level VSI with Synchronized and Symmetrical Waveforms. *IEEE Transactions on Industrial Electronics*, Vol. 54, No. 1, pp. 486-494.

- Celanovic N. and Boroyevich D., 2001. A fast space-vector modulation algorithm for multilevel three-phase converters. *IEEE Transactions on Industry Applications*, Vol. 37, No. 2, pp. 637-641.

- Chowdhary P.K. and Thakre M.P., 2020. MMC based SRM Drives for Hybrid EV with Decentralized BESS. *International Conference on Electronics, Communications and Aerospace Technology (ICECA)*, pp. 319-325.

- Gupta A.K. and Khambadkone A.M., 2006. A Space Vector PWM Scheme for Multilevel Inverters Based on Two-Level Space Vector PWM. *IEEE Transactions on Industrial Electronics*, Vol. 53, No. 5, pp. 1631-1639.

- Hu H., Yao W. and Lu Z., 2007. Design and Implementation of Three-Level Space Vector PWM IP Core for FPGAs. *IEEE Transactions on Power Electronics*, Vol. 22, No. 6, pp. 2234-2244.

- Ibrahim Z.B., Hossain M.L., Talib M.H.N., Mustafa R. and Mahadi M.N., 2014. A five-level cascaded H-bridge inverter based on Space vector pulse width modulation technique. *IEEE Conference on Energy Conversion (CENCON)*, pp. 293-297.

- Kouro S., Malinowski M., Gopakumar K., Pou J., Franquelo L.G. and Rodriguez J., 2010. Recent Advances and Industrial Applications of Multilevel Converters. *IEEE Transactions on Industrial Electronics*, Vol. 57, No. 8, pp. 2553-2580.

- Manasa S., Parimala R.V. and Chayapathy V., 2011. Advanced pulse width modulation techniques for cascaded multilevel Inverters. *International Conference on Sustainable Energy and Intelligent Systems (SEISCON)*, pp. 259-265.

- Mohamed A., Gopinath A. and Baiju M.R., 2009. A Simple Space Vector PWM Generation Scheme for Any General n-level Inverter. *IEEE Transactions on Industrial Electronics*, Vol. 56, No. 5, pp. 1649-1656.

- Maurya D.S., Jadhav P.D., Joshi R.S., Bendkhale R.R. and Thakre M.P., 2020. A Detailed Comparative Analysis of Different Multipulse and Multilevel Topologies for STATCOM. *International Conference on Electronics and Sustainable Communication Systems (ICESC)*, pp. 1112-1117.

- Prasad K.N.V., Misra B. and Surekha J., 2017. A modified space vector algorithm for 5-level cascaded multilevel inverter. *Innovations in Power and Advanced Computing Technologies (i-PACT)*, pp. 1-6.

- Ray R., Shadh M.A. and Reza M.S., 2019. Cascaded H-Bridge Multilevel Inverter Using SVPWM Modulation. *International Conference on Advances in Science, Engineering and Robotics Technology (ICASERT)*, pp. 1-5.

- Rodriguez J., Bernet S., Wu B., Pontt J.O. and Kouro S., 2007. Multilevel Voltage-Source-Converter Topologies for Industrial Medium -Voltage Drives. *IEEE Transactions on Industrial Electronics*, Vol. 54, No. 6, pp. 2930-2945.

- Rodriguez J., Franquelo L.G., Kouro S. and Perez M.A., 2009. Multilevel Converters: An Enabling Technology for High-power Applications. *In proceedings of the IEEE*, Vol. 97, No. 11, pp. 1786-1817.

- Rodriguez J., Lai J.S. and Peng F.Z., 2002. Multilevel inverters: a survey of topologies, controls, and applications. *IEEE Transactions on Industrial Electronics*, Vol. 49, No. 4, pp. 724-738.

- Rushiraj G.J. and Kapil P.N., 2016. Analysis of different modulation techniques for multilevel inverters. *International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT)*, pp. 3017-3024.

- Sabarad J. and Kulkarni G.H., 2015. Comparative analysis of SVPWM and SPWM techniques for multilevel inverter. *International Conference on Power and Advanced Control Engineering (ICPACE)*, pp. 232-237.

- Sanjay P.S., Tanaji P.R. and Patil S.K., 2018. Symmetrical Multilevel Cascaded H-Bridge Inverter Using Multicarrier SPWM Technique. *International Conference for Convergence in Technology (I2CT)*, pp. 1-4.

- Seo J.H., Choi C.H. and Hyun D.S., 2001. A new simplified space-vector PWM method for three-level inverters. *IEEE Transactions on Power Electronics*, Vol. 16, No. 4, pp. 545-550.

- Srivastava S. and Chaudhari M.A., 2020. Comparison of SVPWM and SPWM Schemes for NPC Multilevel Inverter. *IEEE International Student's Conference on Electrical, Electronics and Computer Science (SCEECS)*, pp. 1-6.

- Thakre M.P. and Borse P.S., 2020. Analytical Evaluation of FOC and DTC Induction Motor Drives in Three Levels and Five Levels Diode Clamped Inverter. *International Conference on Power, Energy, Control and Transmission Systems*, pp. 1-6.

- Thakre M.P., Jadhav T.K., Patil S.S. and Butale V.R., 2021. Modular Multilevel Converter with Simplified Nearest Level Control (NLC) Strategy for Voltage Balancing Perspective. *Innovations in Energy Management and Renewable Resources*, pp. 1-8.

Thakre M., Mane J. and Hadke V., 2020. Performance Analysis of SRM Based on Asymmetrical Bridge Converter for plug-in Hybrid Electric Vehicle. *International Conference on Power, Energy, Control and Transmission Systems (ICPECTS)*, pp. 1-6.

Thakre M.P. and Matale N.P., 2020. Alleviation of Voltage Sag-Swell by DVR Based on SVPWM Technique. *International Conference on Power, Energy, Control and Transmission Systems (ICPECTS)*, pp. 1-6.

Wu X., Xiong C., Yang S. and Feng X., 2020. A Simplified Space Vector Pulse Width Modulation Scheme for Three-phase Cascaded H-Bridge Inverters. *IEEE Transactions on Power Electronics*, Vol. 35, No. 4, pp. 4192-4204.

#### **Biographical notes**

Nishant P. Matale received B.E. in Electrical Engineering and M.E. in Electrical Power System from Savitribai Phule Pune University, Maharashtra, India in 2019 and 2021, respectively. His research interests include power system protection, power quality, IOT and FACTS devices.

**Dr. Mohan P. Thakre** received Ph.D. from Visvesvaraya National Institute of Technology, Nagpur, India in 2017. Currently, He is an Assistant Professor in the Department of Electrical Engineering, K.K Wagh Institute of Engineering Education and Research, Nashik, India. His current area of research includes power system protection, FACTS devices, Numerical relaying, power electronics and power quality. He is a senior member of IEEE.

Payal S. Borse received B.E. in Electrical Engineering and M.E. in Electrical Power System from Savitribai Phule Pune University, Maharashtra, India in 2019 and 2021, respectively. Her research interests include FOC and DTC motor drives, power electronics, IOT and FACTS devices.