**ISSN 1112-9867**

Available online at http://www.jfas.info

# A NOVEL METHOD TO DESIGN VARIABLE GAIN AMPLIFIER

S. Mahdavi\*<sup>1</sup>, A. Soltani<sup>1</sup>, M. Jafarzadeh<sup>1</sup> and T. Moradi Khanshan<sup>2</sup>

<sup>1</sup>Department of Microelectronics Engineering, Urmia Graduate Institute, Urmia, Iran

<sup>2</sup>Department of Electrical Engineering, Urmia University, Urmia, Iran

Published online: 19 June 2016

# ABSTRACT

A novel method to design of Variable gain Amplifiers (VGAs) is proposed. A low power VGA with wide range of gain variation and appropriate bandwidth using new technique is presented in this paper. Moreover, the suggested circuit is simulated in whole process corners and different temperatures in the region of -50 to +70 °C. The circuit has been designed in a typical 0.35µm CMOS process with a power supply of 3.3V, and simulated by HSPICE software using level 49 parameters (BSIM3v3).

**Keywords:** variable gain amplifier; Operational Transconductance Amplifier; wide gain range; low power; unity gain bandwidth.

Author Correspondence, e-mail: m.s.mahdavi@urumi.ac.ir

doi: http://dx.doi.org/10.4314/jfas.v8i2s147

# **1. INTRODUCTION**

Variable Gain Amplifiers (VGAs) play a significant role as an analog building block in systems like, disk drives, wireless communication links, signal processing chips and data converters [1]. In a disk drive, a VGA helps to stabilize the voltage supplied to the detector and filter section of a read channel or in wireless communication systems, there is a great deal of variation in received signal strength due to channel fading which should be compensated

using VGA. Fundamentally, the VGA is used in an AGC loop and the loop adjusts the gain of the VGA to produce stable output signal amplitude [2]. Meanwhile, the VGA is very useful module in Radio Frequency (RF) applications in where it serves as a universal purpose gain block to adjust the overall gain of a transceiver which may be affected from manufacturing tolerances or other blocks influence in the system. Some of VGAs use a fixed gain amplifier followed by a variable attenuator to control the gain [3]. In other works, the main amplifier parameters are supposed to change. This paper is organized as follows: in section 2; conventional design is presented. Different Operational Transconductance Amplifiers are stated in section 3; Proposed Method to Achieve Variable Transconductance is indicated in section 4; in section 5 the Proposed Variable Gain Amplifier Circuit is presented; Simulation results are conferred in section 6; and finally section 7 concludes the paper.

#### 2. CONVENTIONAL DESIGN

Conventionally, different methods are utilized to design variable gain amplifier. One of the popular structures is Programmable Gain Amplifier (PGA). Using capacitor and resistor arrays in the feedback path of an op-amp, PGA creates some digital gain levels.

Generally, gain variations could be achieved through variation in amplifier Transconductance or its output resistance. For a MOS Differential Pair (DP) operating in saturation region having tail current source changed leads to alter in DP Transconductance [4].

Equations (1) and (2) demonstrate the concept.

$$g_{m=}\sqrt{(2 \times KP \times (W/L) \times I_{bias})}$$

(1)

$$A_v = G_m \times R_{out}$$

<sup>(2)</sup>

Where Av, Rout and  $g_m$  are DC gain, output resistance and corresponding Transconductance of the amplifier respectively and  $I_{bias}$  represents the tail current source.

As an instance, according to (1) a 30dB change in the gain requires a dramatic change in bias current about 1000 times. The larger current means the more power consumption, especially for high output dynamic ranges.

Moreover, a MOS transistor operating in linear region between the output nodes may be used to have a variable resistance at the output nodes. On the other hand, the achievable gain range is one of the important parameters of the VGA. Typical values for this parameter may vary from 0 dB to 40dB. Beside a wide gain range, there are some other issues such as, high noise immunity, low 3rd-order (IM3) distortion, and required bandwidth which should be addressed. To achieve high linearity, the first rational choice may be the negative feedback structure. However, the limited speed of CMOS process compared to that of BiCMOS or BJT technologies may obscure this approach. Using openloop structures may satisfy speed requirements but has several issues to be settled down. First, the gain of the amplifier needs to be stabilized within a certain range ( $\pm$ 3dB). Though the gain requirement for the amplifier is not very tight, it should not vary too much over process variations and temperatures, which is usually the case if the gain of the amplifier depends on the Transconductance of the devices. Second, the amplifier needs to be linearized out of MOS transistors' inherently nonlinear characteristics. This is more problematic in modern small-feature size processes that pose more short-channel effects and deviate from the classic square-law equation [5,6].

## 3. DIFFERENT OPERANTIONAL TRANSCONDUCTANCE AMPLIFIERES

Among numerous analog circuits, Operational Transconductance Amplifier (OTA) plays a significant role in different systems. It is an important building block of almost all analog and mixed-mode circuits, such as switched-capacitor filters and data converters. OTA is basically an op-amp without an output buffer which is used to drive large capacitive loads. Some of its main characteristics are Gain, Unity Gain Bandwidth, Phase margin, Output swing, Slew rate, CMRR, and PSRR. Single stage fully differential op-amps are usually used to attain higher unity gain frequency owing to their fewer number of poles compared to that of the multiple stage op-amps. Since in single stage amplifiers wholly expected gain is to be achieved in one stage, cascode structure would be a choice to get higher gain. Telescopic cascode and folded cascode structures are two known instances.

In order to achieve high gain, as discussed, the differential telescopic topology can be used. The telescopic architecture is a candidate for a low power, low noise and high gain OTA [7]. The performance of simple telescopic OTA is limited by its input and output voltage swing. However, it provides high gain as well as high speed. As a result, this structure is not good idea for systems with low supply voltages. In order to surmount some drawbacks of telescopic operational amplifier, a folded cascode OTA can be used. Although it consumes more power compared to telescopic cascode, it provides higher output swing. Additionally, this structure sustains high gain and bandwidth as well as convenient voltage headroom for systems with low supply voltages [8]. Furthermore, it allows choosing proper overdrive voltage of transistors to achieve desired unity gain frequency, without affecting the output swing. Also, it is easy to frequency compensate a folded cascode op-amp (the load capacitor operates as compensation capacitor too) rather than a two stage op-amp. In this paper PMOS transistors are used at the input stage of the op-amp thanks to lower noise, body effect elimination, by connecting the body to the source terminal in the n-well technology, and covering negative rail (or ground) by single supply [9].

### 4. PROPOSED METHOD TO ACHIEVE VARIABLE TRANSCONDUCTANCE

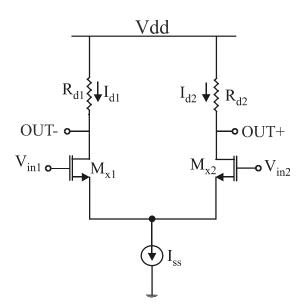

This section is dedicated to explain the proposed idea. Initially the basic concept of the variable gain amplifier is illustrated briefly. Then on the basis of some figures and equations the suggested idea for VGA is outlined. According to Fig.1 the output branches' current is calculated as [10].

$$\Delta id = \frac{1}{2} \mu_n C_{OX} \frac{W}{L} (\Delta vin) \sqrt{\frac{4I_{SS}}{\mu_n C_{OX} \frac{W}{L}}}$$

(3)

$$\Delta \mathrm{id} = I_{D_1} - I_{D_2} \tag{4}$$

$$\Delta \text{vin} = vin1 - vin2 \tag{5}$$

Fig.1. A simple differential pair amplifier

Where  $\Delta id$  and  $\Delta vin$  are the differences of the output branches 'current and the input nodes' voltage respectively.

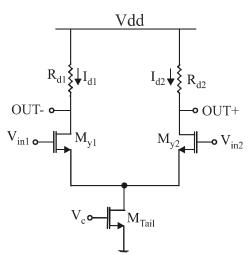

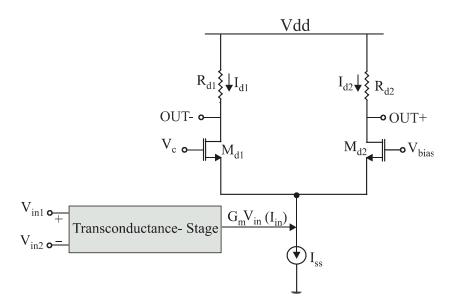

As equation (3) shows  $\Delta idis$  depend on both  $\Delta vin$  and Iss. As a result, there are two approaches to attain a variable current at the output nodes. In the common method the output current is changed through altering the bias current. A simple illustration of this method is depicted in Fig.2 where V<sub>c</sub> is used to modulate tail current in order to generate variable transconductance.

Fig.2. A simple differential pair amplifier with variable bias current

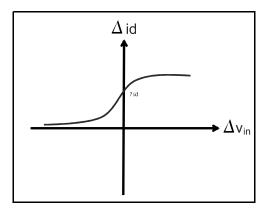

As Fig.3 shows that there is initial relationship between the differential output current and

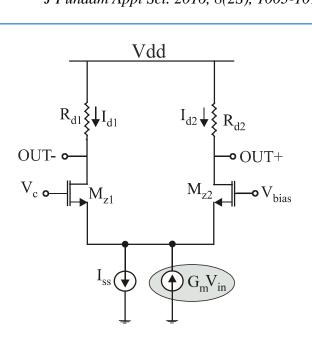

input voltage. Accordingly, modifying  $\Delta v$  will cause variation in $\Delta id$ . To exploit this advantage in the proposed scheme, input signal is applied in current mode. Therefore, as Fig.4 shows to realize this notion, an ac current source which is to represent the output of Transconductance stage is added in parallel with the tail current source. Furthermore, Fig.5 summarises what has been discussed. To make the notion clear, equation (3) is manipulated by replacing IsswithG<sub>m vin</sub>.

$$\Delta \text{vin} = V_c - V_{bias} \tag{6}$$

$$Iss \rightarrow Iss - G_m v_{in} \tag{7}$$

the overall transconductance of the system  $G_m$  can be rewritten as (8).

$$G_{\rm m} = \frac{\partial \Delta I_{\rm D}}{\partial \Delta V_{in}} = \frac{1}{2} \mu_{\rm n} C_{\rm OX} \frac{W}{L} \frac{\frac{4(Iss - G_{\rm m vin})}{W} - 2(V_c - V_{bias})^2}{\sqrt{\frac{4(Iss - G_{\rm m vin})}{\mu_{\rm n} C_{\rm OX} \frac{W}{L}} - 2(V_c - V_{bias})^2}}$$

(8)

where  $V_c$  is applied as a control voltage on some devices to achieve a variable gain. Iss is bias current and  $G_m v_{in}$  is the output current of the input transconductance stage.

Equation (8) clarifies that  $G_m$  is depending on  $(V_c - V_{bias})$  and claims a variable transconductance. What has been argued is a general method and it may be applied on different platforms. As an example, in the next section this method is used on a folded cascode op-Amp to create a variable gain amplifier.

**Fig.3.** Relation of the  $\Delta$ id and  $\Delta$ vin

Fig.4. A differential pair amplifier which input signal is applied in current mode

**Fig.5.** The output of the transconductance stage is added in parallel with the tail current source.

# 5. PROPOSED VARIABLE GAIN AMPLIFIER CIRCUIT

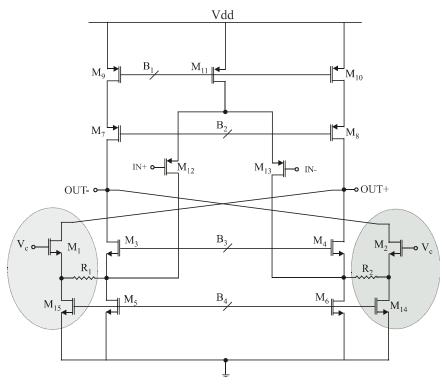

The proposed variable gain amplifier circuit is shown in Fig6.

The main purpose of the proposed structure is to transfer a portion of the output current of the transconductance stage to the output nodes. Also, according to the previous section (4) the overall Gm of the amplifier is controlled by external voltage ( $V_c$ ) which is applied to current source transistors M1 and M2. Since in the proposed structure the gain of the amplifier is

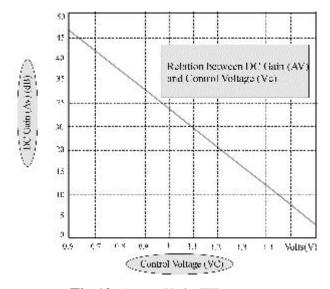

controlled by adjusting the newly added differential pair's  $\Delta v$  (M1-4), the amplifier's gain is independent of the output signal's magnitude. Furthermore, the suggested structure is so efficient in some parameters such as DC gain, unity gain bandwidth. In the proposed simple circuitry just by altering the control voltage ( $V_c$ ) in M1 and M2 it is possible to obtain wide range of DC gain (0dB-47dB) and fine unity gain bandwidth. Also, with varying the size of the M1 and M2 it is possible to achieve negative gain too. Besides, the resistors R1 and R2 are placed to achieve wide range of control voltage ( $V_c$ ), to maintain M1 and M2 in the saturation region, and to obtain positive gain of the proposed circuit, in case that negative gain is not desired. Meanwhile, it is obvious that by using a positive feedback circuit at the output, gain range would be increased. Consequently, the proposed circuit brings about features like wide gain range with acceptable linearity, suitable bandwidth, and possibility to reach both positive and negative gain all together.

Fig.6. The proposed VGA circuit

#### 6. SIMULATION RESULTS

In this section, simulation results of the proposed variable gain amplifier are shown. The circuit has been designed in a typical 0.35µm CMOS process with a power supply of 3.3V,

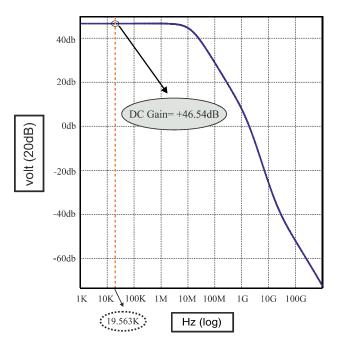

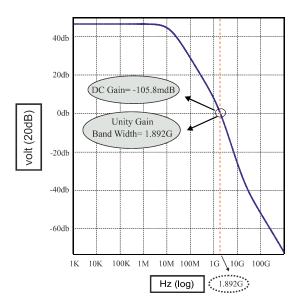

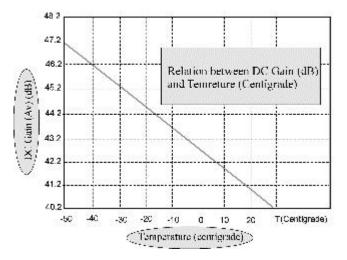

and simulated by HSPICE software using level 49 parameters (BSIM3v3). Fig.7 shows the ac simulation of the proposed VGA for  $V_c$  in which it reaches maximum gain. Also unity gain bandwidth of the amplifier is presented in Fig.8; the diagrams of the  $A_v$  versus  $V_c$  and temperature are sketched using MATLAB in Fig.9 and Fig.10 separately. The DC gain, power consumption, and Unity Gain Bandwidth (UGBW) are given in Table.1 for all corners and within temperatures in the region of -50 to 70 °Cf. In the meantime, to avoid complexity, the temperature is not included in the table and only results of the worst case temperatures are shown. Table.2 performs a comparison between the proposed scheme and previous works.

Fig.7. Ac simulation for maximum gain

Fig.8. Unity gain bandwidth of the amplifier in TT corner.

Fig.9.  $A_v$  vs. T in TT corner

Fig.10.  $A_v$  vs.  $V_c$  in TT corner

Table 1. The results of the Dc gain, power consumption and Unity Gain Bandwidth (UGB)

| Parameters | TT    | SF    | SS   | FF    |

|------------|-------|-------|------|-------|

| Vc(v)      | 0.78  | 0.9   | 0.9  | 0.68  |

| Av (dB)    | 46.54 | 46.26 | 46.3 | 44.36 |

| UGBW(GHz)  | 1.89  | 1.93  | 1.8  | 2.55  |

| Power(mw)  | 8.78  | 9     | 8.49 | 11.1  |

| Table 2. | Comparison | n of VGA | performance |

|----------|------------|----------|-------------|

|          |            |          |             |

| Ref.         | Tech.   | -3dB power     |         | Gain-range(dB) |

|--------------|---------|----------------|---------|----------------|

|              |         | bandwidth(MHz) |         | /stage number  |

| [2]          | 0.5 μm  | 300            | 22mw    | 18/1           |

| [6]          | 1.2 µm  | 25             | 19mw    | 20/1           |

| [11][12][13] | 0.35 µm | 125            | 21mw    | 19/1           |

| This work    | 0.35 µm | 2.5            | 10.5mw  | 60/3           |

|              | 0.18 µm | 20             | 2.43mw  | (-10 to 20)/1  |

|              | 0.35 µm | 13             | 8.7mw   | (0 to 47)/1    |

|              | 0.35 μm | 15             | 8.7111W | (0 10 47)/1    |

## 7. CONCLUSION

A Novel method to achieve variable transconductance is presented. Also this method is implemented on a folded cascode OTA to realize a low power VGA with wide gain variation range and finally spice simulation results have been presented to verify the claims. The proposed algorithm may be used on different platforms to mitigate different requirements of a VGA.

### 8. REFERENCES

[1] Chen .Z, Member, IEEE, Y. Zheng, Member, IEEE, F. Choong, and M. Je, Member, IEEE "A Low-Power Variable-Gain IEEE TRANSACTION ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, VOL. 59, NO. 10, OCTOBER 2012.

[2] Kh. Hadidi and H. Kobayashi, "A 25MHz 20dB Variable Gain Amplifier," 0-7803-1880-3/94/\$4.00 01994 IEEE.

[3] S. Kim, H.-C. Kim, D.-H. Kim S. Jeon, M. Kim and J.S. Rieh," 58–72 GHz CMOS wideband variable gain low-noise amplifier," ELECTRONICS LETTERS 4th August 2011 Vol. 47 No. 16.

[4] Student No. : 981668460Prepared by: Raymond S. P. Tam Submitted to: Prof. PhangDate: November 15, 2002, "CMOS Variable Gain Amplifier (VGA)," ECE1352F AnalogCircuit Design I.

[5] Y. Tang and R. Geiger, "A HIGHLY LINEAR CMOS AMPLIFIER FOR VARIABLE GAIN AMPLIFIER APPLICATIONS,"

[6] Kh. Hadidi, M. Jenabi, J. Sobhi, A. Hasankhaan, "A 300 MLIHZ 18dB Variable Gain Amplifier," 0-7803-5008-1/98/\$10.0001998 IEEE.

[7] K.Gulati and Ha. Lee, Fellow, IEEE "A High-Swing CMOS Telescopic Operational Amplifier," IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 33, NO. 12, DECEMBER 1998.

[8] S. Sharma, P. Kaur, T. Singh, M. Kumar, "A Review of Different Architectures of Operational Transconductance Amplifier," ISSN: 2230-7109 (Online) | ISSN: 2230-9543 (Print) [9] T. Moradi, S. Naghavi, M. Nematzade, K. Hadidi, A.Abrishamifar, A. Khoei, "a fast and low settling error continuous-time common-mode feedback circuit based on differential difference amplifier," December 30, 2013 14:38 wspc / instruction file ws-jcsc

[10] B. Razavi, "Design of analog integrated CMOS circuits book,"

[11] C.-C.Hsu and J.-T. Wu, "A highly linear 125-MHz CMOS switched resistor programmable-gain amplifier," IEEE J. Solid-State Circuits, vol. 38, no. 10, pp. 1663–1670, Oct. 2003.

[12] Y. Zheng, J. Yan, and Y. P. Xu "A CMOS VGA with DC offset cancellation for directconversion receivers, " IEEE Trans. Circuits Syst. I,Reg. Papers, vol. 56, no. 1, pp. 103–113, Jan. 2009.

[13] S.-C. Tsou, C.-F. Li, and P. C. Huang, "A low-power CMOS linear-in -decibel variable gain amplifier with programmable band width and stable group delay," IEEE Trans. Circuits Syst. I, Reg. m Papers, vol. 53, no. 12, pp. 1436–1440, Dec. 2006

## How to cite this article:

Mahdavi S, Soltani A, Jafarzadeh M, Moradi Khanshan T. A novel method to design variable gain amplifier. J. Fundam. Appl. Sci., 2016, *8*(2*S*), *1003-1015*.