# SPACE VECTOR PULSE WIDTH MODULATION OF A MULTI-LEVEL DIODE CLAMPED CONVERTER WITH EXPERIMENTAL VERIFICATION

C.O. Omeje<sup>a</sup>, C.I. Odeh, D.B. Nnadi, M.U. Agu, E.S. Obe

Department of Electrical Engineering, University of Nigeria, Nsukka, Nigeria.

<sup>a</sup>(**Email:** omejecrescent@yahoo.com)

#### Abstract

This paper presents the analysis of a multi-level diode clamped converter (DCC) which is implemented using space-vector pulse width modulation (SVPWM) technique, widely considered as the most efficient and easily applied modulation technique in most industrial drives and control applications. It also focuses on the step by step development of MATLAB /SIMULINK modeling of the space vector pulse-width modulation and the spectral analysis of the resultant waveforms obtained from the modulation results were carried out. Results of the simulations obtained from DCC using SVPWM were equally presented and analyzed. This paper used generic on-time application method to realize the application time for the zero vector and two adjacent active vectors in determining the switching process of the multilevel DCC, quite unlike the look-up table which is common in this area. To verify the analysis, a small scale experimental work, was carried out. All experimental works were done in the laboratory and the results confirm the simulation results obtained from the SIMPLORER Student version 6 Software used in simulating the un-modulated three-level diode clamped converter.

Keywords: ,,,,,

#### 1. Introduction

Space vector pulse width modulation (SVPWM) is a modulation technique that involves the generation of a reference vector  $V_{ref}$  representing a three phase sinusoidal voltage which is realized by switching between two nearest active vectors and one zero vector switching sequence of a power converter [1]. SVPWM-based multi-level converters have gained great advantages in high power and high performance industrial drive application. This is because of their inherent digital application, efficient D.C bus voltage utilization through a D.C capacitor voltage

balance strategy, lower dv/dt stresses that result from the D.C capacitor voltage balance across the inverter D.C voltage bus-bar, a reduced electromagnetic interference (EMI) due to reduced switching frequency losses, a minimized total harmonic distortion corresponding to a low inverter switching frequency  $f_{sw}$  [2].

### 2. Principles of Operation of a Multi-Level Diode Clamped Converter

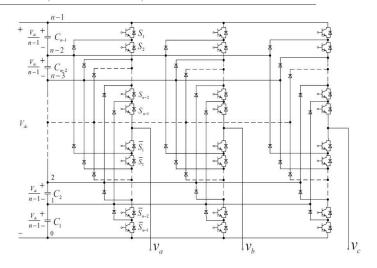

The operation of a multi-level diode clamped converter using a schematic diagram of a three phase *n*-level DCC

with a DC-linking capacitors ranging from  $C_1, C_2, C_3, \ldots, C_{n-2}$  to  $C_{n-1}$  is presented here. Corresponding to this net DC-link is a D.C voltage Vdc which is evenly distributed along the (n-1) D.C capacitors bus.

The D.C voltage across each capacitor bus is numerically given by  $V_{dc}/(n-1)$ [3]. Each leg of the n-level diode clamped converter (DCC) consists of 2(n-1) active switches with anti-parallel diodes and (n-2) pairs of clamping diodes. are (n-1) complementary switch pairs in each phase leg which determine the basic operations of a multi-level DCC [3]. For all complementary switch pairs, the routinely turning ON of one switch excludes the other from being turned ON. Using phase A as an example, the (n-1) complementary switch pairs for an *n*-level inverter are  $(\overline{S_1}, S_1), (\overline{S_2}, S_2), (\overline{S_3}, S_3), \ldots, (\overline{S_{n-2}}, S_{n-2})$ and  $(\overline{S_{n-1}}, S_{n-1})$ . Therefore, turning ON  $S_1, S_2, S_3, \ldots, S_{n-2}$  and  $S_{n-1}$ , excludes  $\overline{S_1}, \overline{S_2}, \overline{S_3}, \ldots, \overline{S_{n-2}}, \text{ and } \overline{S_{n-1}} \text{ from being}$ turned ON as shown in Fig. 1, which represents the schematic diagram of a three phase n-level DCC.

From Fig. 1, node 0 voltage is considered as the reference voltage. The switching combinations for *n*-level inverter required to synthesize the different voltage levels are summarized in table 1 below.

# 3. Space Vector Voltage States representation of 3, 4 and 5 level DCC

The space vector representation of the above multi-level inverter is conveniently done by determining the possible switching states of an n-level inverter. This is realized from the fact that for all n-level inverter the possible number of switching state is obtained from the following relation:

$$N = n^{\phi} \tag{1}$$

Where n represents the voltage level and  $\phi$  represents the number of phase which in this context is three. The switching voltage states

Figure 1: Circuit Diagram of a three phase n-level DCC.

when normalized as  $V_{dc}$  or in its per unitized value always take a range from 0 to n-1 [4]. In this switching voltage states, there exist an active and a redundant switching states. The active switching states are those power converter switching states that have unique and distinct space vector value in  $\alpha - \beta$  plane. While the redundant switching states are those converters switching states that give the same space vector value in  $\alpha - \beta$  plane in other words, they have no unique space vector value in  $\alpha - \beta$  plane [4].

For ease in the determination of the number of redundant voltage states, active voltage states and number of voltage level, the formulae tabulated below are used in achieving this objective [4].

The actual representation of the 3, 4 and 5 level DCC in space vector is realized by the determination of the line voltages, phase voltages and the  $\alpha-\beta$  di-phase voltages along the  $\alpha-\beta$  frame using the Park's and Clark's transformations as well as the balanced system voltage expression. For a balanced system, the phase voltages are given by the fol-

|                  |       | Table | e 1: 5 | witchir   | ig state  | S OI 8           | an $n$           | ievei . | Dioae c              | ampea                | converter.                |

|------------------|-------|-------|--------|-----------|-----------|------------------|------------------|---------|----------------------|----------------------|---------------------------|

| Switching States | $S_1$ | $S_2$ |        | $S_{n-2}$ | $S_{a-1}$ | $\overline{S}_1$ | $\overline{S}_2$ |         | $\overline{S}_{n-2}$ | $\overline{S}_{n-2}$ | Phase Voltage             |

| I                | 1     | 1     |        | 1         | 1         | 0                | 0                |         | 0                    | 0                    | $V_{dc}$                  |

| II               | 0     | 1     |        | 1         | 1         | 1                | 0                |         | 0                    | 0                    | $(n-2)\frac{V_{dc}}{n-1}$ |

|                  |       |       |        |           |           |                  |                  |         | •                    |                      |                           |

|                  |       |       |        |           |           |                  |                  |         | •                    |                      |                           |

| •                |       |       |        |           |           |                  |                  |         |                      |                      |                           |

| n-2              | 0     | 0     |        | 0         | 1         | 1                | 1                |         | 1                    | 0                    | $2\frac{V_{dc}}{n-1}$     |

| n = 1            | 0     | Ω     |        | Ω         | 0         | 1                | 1                |         | 1                    | 1                    | 0                         |

Table 1. Switching states of an n-level Diode clamped converter

lowing matrix expression:

$$\begin{bmatrix} V_{an} \\ V_{bn} \\ V_{cn} \end{bmatrix} = \begin{bmatrix} 2/3 & -1/3 & -1/3 \\ -1/3 & 2/3 & -1/3 \\ -1/3 & -1/3 & 2/3 \end{bmatrix} \times \begin{bmatrix} V_{ao} \\ V_{bo} \\ V_{co} \end{bmatrix}$$

(2)

From the above matrix, the corresponding lines to neutral voltages are given as follows:

$$V_{an} = \frac{2}{3} \times V_{ao} - \frac{1}{3} \times (V_{bo} + V_{co})$$

(3)

$$V_{bn} = \frac{2}{3} \times V_{bo} - \frac{1}{3} \times (V_{ao} + V_{co})$$

(4)

$$V_{cn} = \frac{2}{3} \times V_{co} - \frac{1}{3} \times (V_{ao} + V_{bo})$$

(5)

The Park's tranformation is given by:

$$[F_{qdo}]^t = [T_{qdo}] \times [F_{abc}]^t \tag{6}$$

Where,

$$T_{qdo} = \frac{2}{3} \times \begin{bmatrix} \cos \theta & \cos \left(\theta - \frac{2\pi}{3}\right) & \cos \left(\theta + \frac{2\pi}{3}\right) \\ -\sin \theta & -\sin \left(\theta - \frac{2\pi}{3}\right) & -\sin \left(\theta + \frac{2\pi}{3}\right) \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix}$$

$$(7)$$

$\theta$  represents the angle of the orthogonal sets of q-d-o in their arbitrary reference frame. The above (7) holds if the positive q-axis leads the positive d-axis by 900, but if the positive q-axis lags behind the positive d-axis by 900, then the negative sign in the second row of the above matrix in (7) changes to positive. For a stationary reference frame,  $\theta$  in (7) tends to zero since q-axis is aligned with the stator q-axis [5]. Under this condition, (7) changes to the Clarks transformation matrix given by (8) [5].

$$\begin{bmatrix} F_{\alpha s} \\ F_{\beta s} \\ F_{os} \end{bmatrix} = \frac{2}{3} \times \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \times \begin{bmatrix} F_{as} \\ F_{bs} \\ F_{cs} \end{bmatrix}$$

(8)

Table 2: Determination of the active and redundant voltage state for the different levels.

| Number                 | A      | В     | C     | D               | E         |

|------------------------|--------|-------|-------|-----------------|-----------|

| of Inverter<br>Level * |        |       |       |                 |           |

| n-Level                | 6(n-1) | (n-1) | $n^3$ | $n^3 - (n-1)^3$ | $(n-1)^3$ |

| 2-Level                | 6      | 1     | 8     | 7               | 1         |

| 3-Level                | 12     | 2     | 27    | 19              | 8         |

| 4-Level                | 18     | 3     | 64    | 37              | 27        |

| 5-Level                | 24     | 4     | 125   | 61              | 64        |

\* A = Number of switches with anti-parallel Diodes.

${\bf B}={\bf Number}$  of very close switches of each inverter leg required to be in the on- state.

C = Number of different voltage states of the n-inverter.

D = Number of unique voltage states (Active states) of the inverter.

E = Number of the redundant voltage states of the inverter.

For the scope of this work, an improved transformation matrix by Concordia was applied as shown in (9a). Since emphasis is on the di-phase  $\alpha - \beta$  frame, the zero sequence is neglected.

Therefore, the  $V_{\alpha}$  and  $V_{\beta}$  values are derived from (9b) as shown below.

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \\ V_{o} \end{bmatrix} = \sqrt{\frac{2}{3}} \times \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{2} \end{bmatrix} \times \begin{bmatrix} V_{an} \\ V_{bn} \\ V_{cn} \end{bmatrix}$$

$$(9a)$$

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \times \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \times \begin{bmatrix} V_{an} \\ V_{bn} \\ V_{cn} \end{bmatrix}$$

$$(9b)$$

From (9b), the  $V_{\alpha}$  and  $V_{\beta}$  expressions are given as:

$$V_{\alpha} = \sqrt{\frac{2}{3}} \times \left[ V_{an} - \frac{1}{2} \times (V_{bn} + V_{cn}) \right]$$

(10)

$$V_{\beta} = \sqrt{\frac{2}{3}} \times \left[ \sqrt{\frac{3}{2}} \times (V_{bn} - V_{cn}) \right]$$

(11)

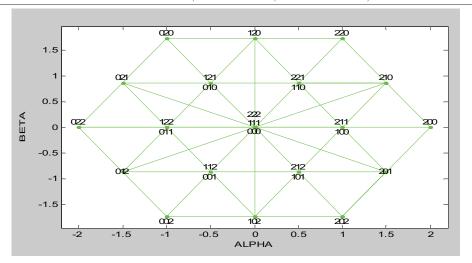

The placement of these multi-level voltage states in their spatial positions for the three

Figure 2: 3- Level Space Vector Voltage States.

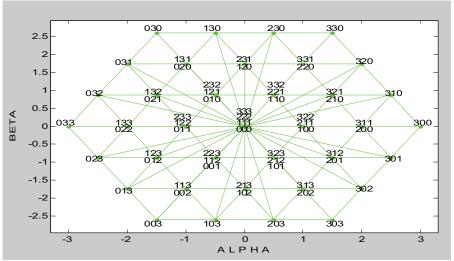

Figure 3: 4- Level Space Vector Voltage States.

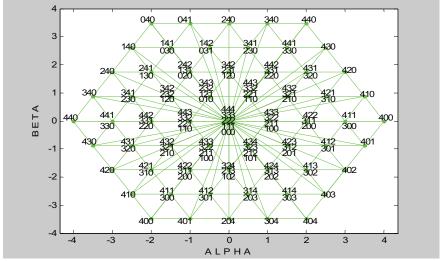

Figure 4: 5- Level Space Vector Voltage States.

different levels is done with consideration to the positions of the voltage levels in the  $\alpha - \beta$  plane derived from the above generated equations. Therefore, for the 3-level, the 27-voltage states are represented in space by the hexagonal display realized by the MATLAB GPLOT command. The results obtained are shown in Fig; 2 for the 3-level space vector voltage states while Figs: 3 and 4 represent the space vector voltage states of the 4 and 5-level inverter in their spatial positions.

### 4. Space Vector Switching On-Time and Reference Voltage Determination

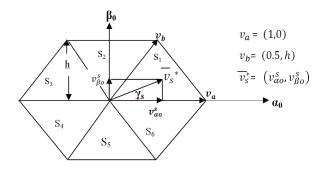

To determine the switching on time and reference voltage of a multi level SVPWM inverter, classical two-level space vector geometry by Gupta is used for this analysis [6].

Figure 5 shows the space vector diagram of a two level inverter. Each of the six sectors that make up this inverter is made up of an equilateral triangle of unity length with a triangular height of  $h=\sqrt{3}/2$  this also forms the height of the sector. Thus, the ON time calculation for any of the six sectors is the same. Considering sector 1 of Fig. 5, it shows that the reference vector  $(\overline{v}_s^*)$  is the vector sum (resultant vector) of  $v_{\alpha o}^s$  and  $v_{\beta o}^s$  [6].

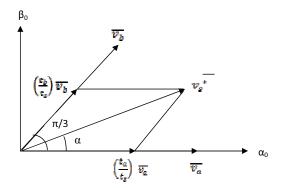

The duty cycle of the switching vectors  $\overline{v}_a$  and  $\overline{v}_b$  are got from (12) and (13), respectively.

$$\overline{v}_s^* = \left(\frac{t_a}{t_s}\right) \times \overline{v}_a + \left(\frac{t_b}{t_s}\right) \times \overline{v}_b \tag{12}$$

$$\overline{v}_s^* \times t_s = t_a \times \overline{v}_a + t_b \times \overline{v}_b \tag{13}$$

$$t_s = t_a + t_b + t_0 \tag{14}$$

Where  $\left(\frac{t_a}{t_s}\right)$  and  $\left(\frac{t_b}{t_s}\right)$  are the duty-cycles of the switching vectors  $\overline{v}_a$  and  $\overline{v}_b$  while  $t_s$  is the sampling time given by the sum of the two active vectors and the zero vector. Similarly,  $t_a$ ,  $t_b$  and  $t_0$  are the application times of the two active vectors and zero vector. The application time and their corresponding voltage

Figure 5: Space vector diagram of two-level inverter.

magnitude are obtained by vector resolution of Figs (5 & 6) along the  $\alpha_o$  and  $\beta_o$  axis and by direct substitution of the values of  $v_a = (1,0)$  and  $v_b = (0.5, h)$  into the equation obtained after vector resolution. The results obtained are given by the following equations:

$$t_a = t_s \times \left( v_{\alpha o}^s - \frac{v_{\beta o}^s}{2 \times h} \right) \tag{15}$$

$$t_b = v_{\beta o}^s \times \frac{t_s}{h^2} \tag{16}$$

$$t_0 = t_s - t_a - t_b (17)$$

$$v_{\alpha o}^s = \overline{v}_s^* \times \cos \gamma_s \tag{18}$$

$$v_{\beta o}^s = \overline{v}_s^* \times \sin \gamma_s \tag{19}$$

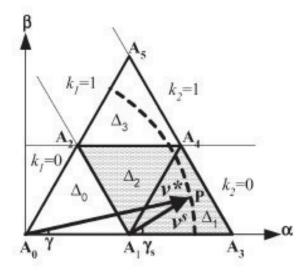

A follow up to the application times for the active and zero vectors is the triangle and sector determination corresponding to the rotation of the reference vector in space; this is realized with consideration to Fig, 7 which represents sector1 of three level space vector diagram.

Sector 1 of Fig. 7 is split into four triangles so do other remaining sectors. These triangles are classified into two types: type 1 and type 2 respectively [6].

A triangle of type 1 always has its base at the bottom and it rests on the  $\alpha$ -axis plane as shown above, the following triangles belong to type1:  $\Delta_0$ ,  $\Delta_1$  and  $\Delta_3$ .

A triangle of type 2 has its base inverted and it points towards the  $\beta$ -axis plane. Triangle that belongs to this class is  $\Delta_2$  with its

Figure 6: Diagram of a space vector duty-cycle calculation.

Figure 7: Space vector triangular determination.

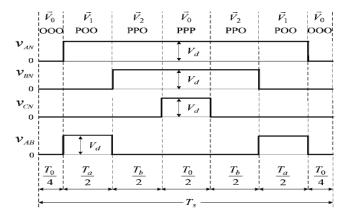

Figure 8: Seven- segment switching sequence for  $V_{ref}$ .

vertex resting on the  $\alpha$ -axis plane as shown in Fig. 7.

The determination of these triangles in the six sectors is effectively done by applying the following equations (20) and (21).

$$K_1 = \text{int}(v_{\alpha a}^s + v_{\beta a}^s / \sqrt{3})$$

(20)

$$K_2 = \operatorname{int}(v_{\beta o}^s/h) \tag{21}$$

$K_1$  represents the part of a given sector lying between two lines that join the vertices of two triangles which is separated by the height of the equilateral triangle (h) and also inclined by 120°C to the  $\alpha$ -axis plane.  $K_2$  represents that part of a sector lying along a horizontal line joining the vertices of two triangles which is separated by the same height of the equilateral triangle (h) but is parallel to the  $\alpha$ -axis plane.  $K_1$  and  $K_2$  are presented in Fig.7 with their corresponding values at different locations of sector 1.

Triangles of type1 and type2 represent sector1 and sector4 of the two level inverter and it is on this assumption that the application time for the zero and the two active vectors  $(t_0, t_a, t_b)$  for other multi-level inverters are calculated since  $t_0, t_a$  and  $t_b$  are functions of  $(v_{\alpha o}, v_{\beta o})$ .

From the reference vector  $v^*$  shown in the Fig 7, the sector of operation and its angle  $(\gamma)$  within this sector is determined by the following equations:

$$Si = \operatorname{int}\left(\frac{\theta}{60}\right) + 1$$

(22)

$$\gamma = \operatorname{rem}\left(\frac{\theta}{60}\right) \tag{23}$$

The angle  $\theta$  represents the angle of the reference vector with respect to the  $\alpha$ -axis plane with range given by 0°C  $< \theta < 360$ °C. While int, as well as rem, represent the MATLAB standard function called integer and remainder for a given mathematical division. The slope of  $\mathbf{A_1P}$  is given by  $v_{\beta i}/v_{\alpha i}$  and the slope of  $\mathbf{A_1A_4}$  is given by:

(Height of equilateral triangle  $\mathbf{A_1}\mathbf{A_3}\mathbf{A_4}$  of unity length)  $\div$  (1/2 of  $A_1A_3$ ) =  $\sqrt{3}$

The result obtained from comparing the two slopes produces the following inequality

$$v_{\beta i} \le \sqrt{3}v_{\alpha i} \tag{24}$$

The relational equations for  $v_{\alpha i}$  and  $v_{\beta i}$  with respect to  $K_1$  and  $K_2$  are given by (24) and (25) respectively.

$$v_{\alpha i} = v_{\alpha o}^s - K_1 + 0.5 \times K_2 \tag{25}$$

$$v_{\beta i} = v_{\beta o}^s - K_2 \times h \tag{26}$$

here  $v_{\alpha o}^s$  and  $v_{\beta o}^s$  are the values of the new active vectors along  $\alpha - \beta$  axes corresponding to the change in the rotation of the reference vector P. From (24) the following condition holds. If  $v_{\beta i} \leq \sqrt{3}v_{\alpha i}$ , then  $v_{\alpha o}^s = v_{\alpha i}$  and  $v_{\beta o}^s = v_{\beta i}$  else  $v_{\alpha o}^s = 0.5 - v_{\alpha i}$  and  $v_{\beta o}^s = h - v_{\beta i}$ . The same analogy of triangle and sector determination for this 3 - level is used for higher level of inverter [6]. For sectors of multi-level inverter with multiple number of triangles  $\Delta_j$ , the triangle types are determined from the following equations (27) and (28):

$$\Delta_j = K_1^2 + 2K_2 \tag{27}$$

$$\Delta_j = K_1^2 + 2K_2 + 1 \tag{28}$$

Equation (27) is used to determine a triangle of type 1 while (28) is used to determine a triangle of type 2. Symmetrical space vector pulse width modulation is achieved by applying the zero state vectors followed by two adjacent active states in half switching period. The next half of this switching period is the mirror image of the first half. The total switching period is divided into seven segments. The zero vectors are always applied for of the total time required by the zero vector duration and this is followed by half of the application time for the active vectors [7]. The sequence continues as indicated in Fig. 8 which formed the basis of the space vector switching pattern used in the on-time calculation sequence.

#### 5. Model Equations for Space Vector Multi- Levels DCC

The equations used in the modeling of a three phase, three level diode clamped converter with respect to the reference vector angle and magnitude are presented below:

$$V_{AN} = \frac{1}{\sqrt{3}} \times V_{LL} \times \cos \omega t \tag{29}$$

$$V_{BN} = \frac{1}{\sqrt{3}} \times V_{LL} \times \cos\left(\omega t - \frac{2\pi}{3}\right) \quad (30)$$

$$V_{CN} = \frac{1}{\sqrt{3}} \times V_{LL} \times \cos\left(\omega t - \frac{4\pi}{3}\right) \quad (31)$$

The space vector voltage is given by

$$V_s = \frac{2}{3} \times (V_{AN} + aV_{BN} + a^2V_{CN})$$

(32)

Where operator  $a = \cos 120^{\circ} + j \sin 120^{\circ}$  and  $a^2 = \cos 240^{\circ} + j \sin 240^{\circ}$ . For a balanced three phase system, the magnitude of the output voltages and their corresponding frequency must be equal. Therefore substituting the values of a an  $a^2$  and with only the corresponding voltage magnitude of the above three phase voltages into (33) produces (34) as shown

$$V_s = \frac{2}{3} \times (|V| + |V| \cos 120^{\circ} + j|V| \sin 120^{\circ} + |V| \cos 240^{\circ} + j|V| \sin 240^{\circ})$$

(33)

Re-arranging (33) into real and imaginary paths produces (34) as shown below:

$$V_s = \frac{2}{3} \times (|V| + |V| \cos 120^{\circ} + |V| \cos 240^{\circ} + j(|V| \sin 120^{\circ} + |V| \sin 240^{\circ}))$$

(34)

Since d-q voltages are orthogonal (right-angled) to each other [8]. Then (34) aligned in the d-q plane produces (35) and (36) respectively.

$$V_d = \frac{2}{3}(|V| + |V|\cos 120^\circ + |V|\cos 240^\circ$$

(35)

$$V_q = \frac{2}{3}(|V|\sin 120^\circ + |V|\sin 240^\circ) \qquad (36)$$

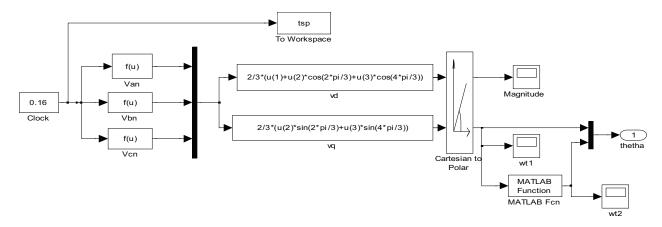

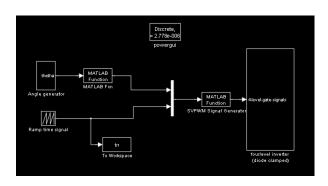

Figure 9: SIMULINK model for theta and magnitude determination of reference vector.

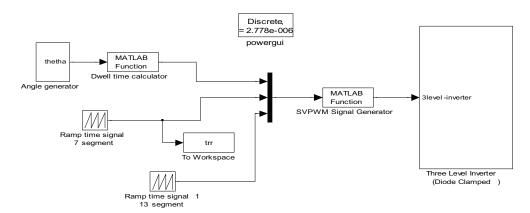

Figure 10: Overall Simulink model for 3-level space vector DCC.

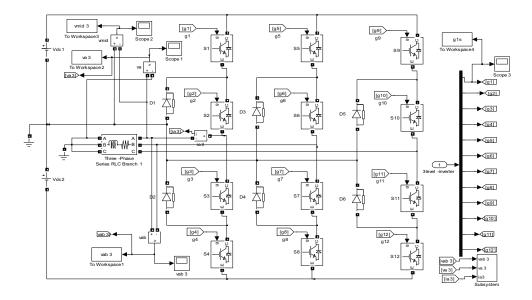

Figure 11: 3-level space vector diode clamped converter.

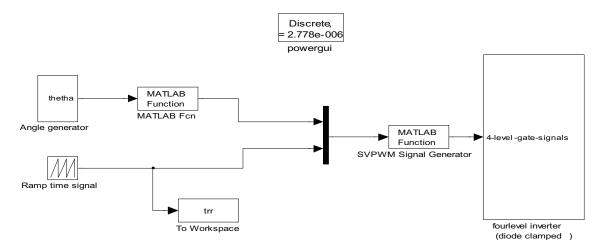

Figure 12: Overall Simulink model for 4-level space vector diode clamped converter.

Figure 13: Overall Simulink model for 5-level space vector diode clamped converter.

Equations (35) and (36) formed the basic equation models for the generation of the reference angle and magnitude of reference vector which is achieved by using the Cartesian to polar block got from transformation block in the SIMULINK extras contained in the SIMULINK sub-library as shown in the SIMULINK model of Fig. 9.

The Overall SIMULINK Models for the 3, 4, and 5 levels Diode Clamped Converter with the subsystem model of 3-level are shown in figures 10 - 13 (refer to Appendix 1).

Figure 14: 4-level space vector diode clamped converter

#### 6. Results of the Simulation for Multi-Levels of SVPWM DCC

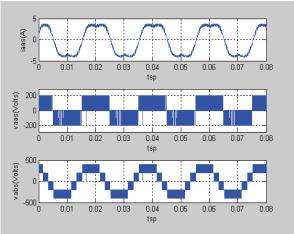

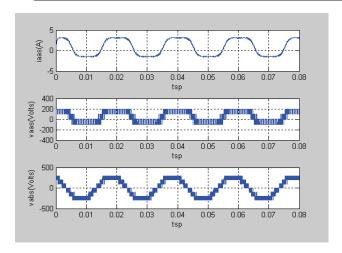

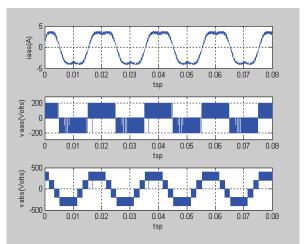

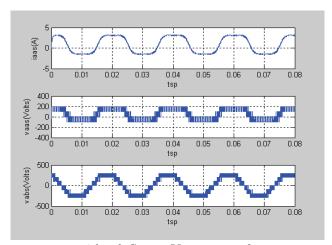

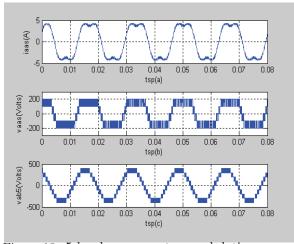

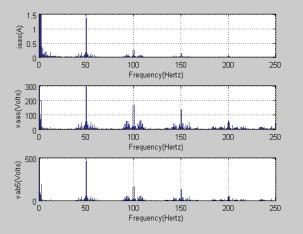

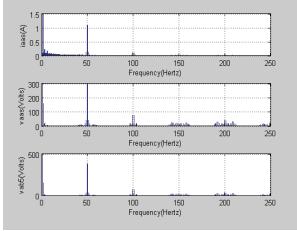

The simulation results (waveforms) for the above multi-level diode clamped converter with their corresponding spectral waveforms at a modulation index of 0.8 are shown below:

### 7. Percentage of Total Harmonic Distortion for the 3, 4 and 5- Level SVPWM Wave-Forms

THD for the phase current = 21%

Figure 15: 5-level space vector diode clamped converter model

Figure 16: 3-Level Space Vector Waveform at a modulation index of 0.8.

Figure 17: 4-level Space Vector waveform at a modulation index 0.8.

Figure 18: 5-level space vector modulation waveform at a modulation index 0.8.

Figure 19: Spectral result of 3-level Space Vector wave at a modulation index 0.8.

Figure 20: Spectral result of 4-level Space Vector wave at a modulation index 0.8.

THD for the phase voltage = 26%

THD for the line voltage = 32%

# Harmonic distortion values for the 4level space vector modulation waveforms

THD for the phase current = 18.2%

THD for the phase voltage = 20.6%

THD for the line voltage = 25.2%

# Harmonic distortion values for the 5level space vector modulation waveforms

THD for the phase current = 14.19%

THD for the phase voltage = 18.93%

THD for the line voltage = 21.42%

# 8. Experimental Verification of Three Level Diode Clamped Converter

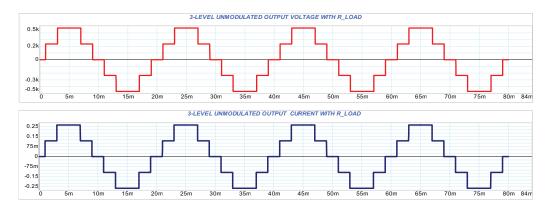

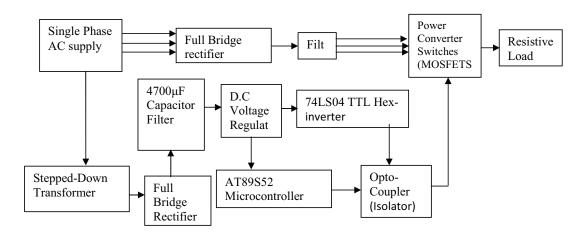

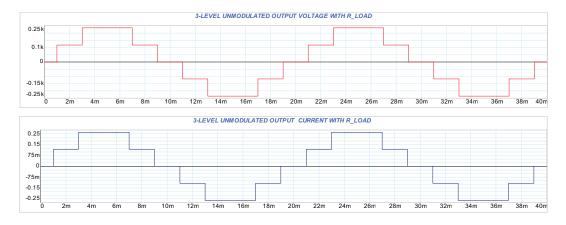

The single phase un-modulated three level DCC was first simulated using simplorer to view the expected laboratory result under a resistive load before the final implementation. The laboratory result was achieved by the following stages presented in the block diagram of Fig 22:

The experimental result for the 3-level un-modulated diode clamped converter with resistive load is shown in oscilloscope screen presented in Fig. 23. This result corresponds with the result obtained from the SIMPLORER simulation for the 3-level un-modulated DCC with a resistive load as shown in Fig. 23.

#### 9. Conclusion

This paper presented a space-vector pulse width modulation (SVPWM) based scheme that performs the modulation of 3, 4 and 5-level DCC at a modulation index of 0.8. The switching ON-time using the generic two-level duty cycle algorithm reduces the time-wasting complex equation analysis and the rigours involved in consulting a look-up table for higher-level DCC ON-time calculation.

Figure 24: 3-Level Laboratory Set-up.

Figure 25: 3-Level Laboratory result.

The simulation results proved that the overall total harmonic distortions as well as the switching Losses are generally reduced as the inverter level increases as shown in the total distortion values. It is also recommended that odd inverter levels such as 3, 5 and more be used in the future analysis since a better analysis and efficient waveforms are derived from these odd inverter as shown in figure 16 and figure 20 respectively.

#### References

J. Rodriguez, J.S Lai and F.Z. Peng. Multilevel Inverters: A Survey of Topologies, Controls and Applications, *IEEE Transac*tion on industrial Electronics, Vol.49, No.4,

Figure 21: Spectral result of 5-level Space Vector wave at a modulation index 0.8.

Figure 22: Block diagram of the three level DCC design.

Figure 23: Spectral result of 4-level Space Vector waveform at a modulation index 0.8.

- PP.724-738, August, 2002.

- H. Lei, H.O. Wang and X. Deng. A Simple SVPWM Algorithm for multi-level Inverters, 35th Annual IEEE Power Electronics Specialist Conference, Aachen, Germany, 2004.

- M. Saeedifard, H. Nikkhajoei, R. Iravani and A. Bakhshai. A Space Vector Modulation Approach For A Multi- Module HVDC Converter System, *IEEE Transactions on Power* Delivery, Vol.22, No.3, PP.1643-1654, July, 2007.

- P. Bhagwa and V. Stefanovic. Generalized Structure of a Multi-level PWM Inverter, *IEEE Transactions on Industrial Ap*plications, Vol.19, No.6, PP.1057-1069, Nov, 1983.

- 5. C.M. Ong. Dynamic Simulation of Electric Machinery Using Mat lab/Simulink. Prentice Hall PTR. Upper Saddle River, New Jersey, 1998.

- A.K. Gupta, A.M. Khambadkone, and K.M. Tan. A two-level Inverter based SVPWM Algorithm for a Multi-level Inverter. In proc. Annual Conference IEEE Industrial Electronic (IECON), Vol.2, No.10, PP.1823-1828, November, 2004.

- 7. D.G. Holmes. The General Relationship between Regular- Sampled Pulse width Modulation and Space Vector Modulation for Hard Switched Converters. In conf. Rec. *IEEE- IAS Annual Meeting*, PP.2482-2488, June, 2000