# OPTIMIZATION OF INSULATED HfO<sub>2</sub> DIELECTRICS OF GaN/InN/GaN/ In<sub>0.1</sub>Ga<sub>0.9</sub>N ENHANCEMENT MODE OF MIS-HEMT HETEROSTRUCTURE FOR HIGH FREQUENCY POWER AMPLIFIER APPLICATIONS

# Y. Tarauni<sup>1,\*</sup>, Y. Shehu<sup>2</sup>, M. Auwal<sup>3</sup> and A. Rakiya<sup>4</sup>

<sup>1, 2, 3, 4</sup>, DEPARTMENT OF PHYSICS, KANO UNIV. OF SCIENCE & TECH., WUDIL – KANO, KANO STATE, NIGERIA. *E-mail addresses:*<sup>1</sup> ytarauni@hotmail.com, <sup>2</sup> ysdanfari@yahoo.com, <sup>3</sup> auwalsafa@gmail.com, <sup>4</sup> yakiyaaliyu23@yahoo.com

## ABSTRACT

In this paper, the enhancement-mode operation of the hetestructure of GaN/InN/GaN/In<sub>0.1</sub>Ga<sub>0.9</sub>N of the Metal Insulator Semiconductor High Electron Mobility Transistor (MIS-HEMTs) device having InN-channel was investigated. The effect of scaling the device dimensions of Metal Insulator, such as the dielectric thickness of HfO<sub>2</sub> and the channel lengths, on the electrical performances was analyzed and compared to the currently used heterostructure. The numerical simulation of synopsis TCAD used showed a significant improvement in the electrical properties of the device that achieved a threshold voltage ( $V_T$ ) = 0.828 maximum drain current of 1.77 A/mm V, transconductance ( $g_m$ ) of 2.29 S.mm<sup>-1</sup>, lowest ON-state resistance ( $R_{ON}$ ) of 0.21  $\Omega$ .mm, and along with high-frequency performance achieving  $f_T$ /  $f_{max}$  of 98 GHz/129 GHz and 200 GHz/ 360 GHz respectively. The simulations also showed that this scaled GaN/InN/GaN/In<sub>0.9</sub>Al<sub>0.1</sub>N heterostructure MIS-HEMT is an excellent substitute to the currently used MIS-HEMTs for delivering high power density and frequency at RF/power amplifier applications.

**Keywords:** Enhancement mode, Hydrodynamic simulation, InN channel, MIS-HEMT, In<sub>0.9</sub>Al<sub>0.1</sub>N barrier/buffer, HfO<sub>2</sub>, T<sub>CH</sub>, Transconductance

## **1. INTRODUCTION**

For nearly 50 years, the microelectronics revolution has been characterized by "smaller is better," the amazing realization that scaling down transistor size leads to increased transistor density, faster switching speed and enhanced power efficiency. A significant turn in this exhilarating ride took place in the last few years. Si CMOS scaling is now in a new phase of "power constrained scaling" in which the power density dissipated by logic CMOS chips has all but hit a limit of about 100 W/cm2 [1]. Power density cannot increase much more without incurring in very substantial packaging and cooling costs that are impractical for most applications. Under power constrained scaling, continued transistor size scaling demands a reduction in operating voltage [2]. Trying accomplish this while enhancing transistor to performance has become increasingly difficult. Partly because of this, the operating voltage for CMOS has bottomed at around 1 V for the last few generations of technology. This hard limit poses a serious threat to further progress.

One way out of this is by introducing a new channel material with a much higher carrier velocity. This would allow further voltage scaling while continuing to enhance performance. A promising family of materials is III-V compound semiconductors. III-Vs are well known for their unique suitability for high frequency electronics. III-V based integrated circuits are now widely used in communications and defense applications. Some of these are mission critical, such as space systems where exceedingly high reliability is essential. Others are mass-market and very costsensitive applications such as low-noise amplifiers and switches for smart phones. Of all alternatives that are being considered to extend the life of CMOS, III-Vs are the only materials with an established manufacturing and reliability record.

High electron mobility transistors (HEMT) based on the III-V semiconductors GaAs and InN are very popular and successful devices for radio frequency and power applications [8]. The operating frequencies of these transistors cover the range from 800 MHz to 1 THz. About 30 years ago, a new HEMT type based on the wide bandgap material GaN has been introduced - the GaN High Electron Mobility Transistors (HEMTs). Since that time, GaN HEMTs have attracted a lot of attention. GaN technology has been steadily improved and each year GaN HEMTs with new RF record performance have been reported. Today, these devices show output power densities superior to any other RF field-effect transistor (FET) type, and are very promising candidates for high-power amplification in the frequency range up to 1 THz (and possibly above). The frequency limits (cut-off frequency and maximum frequency of oscillation,) of GaN HEMTs have been pushed beyond 1 THz recently [11]. The impressing power and frequency performance of GaN HEMTs is due to some unique material properties of the AlGaN/GaN material system.

InN is a unique material with the highest electron velocity among all common semiconductors, about four-times higher than for Si [1, 2]. Consequently, high mobility binary InN-channel transistors may substantially outperform speed performance of Sibased devices. Besides that, InN belongs to a family of III-V semiconductors which are polar materials with an ability to create high-density Two-Dimensional Electron Gas (2DEG) in a quantum well (QW) of highelectron mobility transistors (HEMTs) without intentional doping [3]. InN-based HEMTs may be record fast among III-V transistors. [4,5]. Theoretical analysis has shown that, for ideal transistors with  $L_q =$ 0.1 µm, by replacing the GaN channel with InN, we can expect  $f_7$  to increase from 480 to 880 GHz [6].

There are several advantages associated with GaN based devices, such as lower contact resistance [8], better channel confinement [9], and enhancement mode operation [10]. In conjunction with a strain-free lattice matched InAIN back-barrier confinement layers with record high transconductance and power gain cutoff frequency has been reported [11,12]. Thus, GaN technology has evolved as a viable candidate for an ultra-scaled GaN HEMT technology. Great progress has been made towards good DC and RF performance GaN-based HEMTs. Finally, in the SiN<sub>x</sub>/AlGaN/GaN/AlGaN MISHEMT with ft/fmax of

103/196 for  $V_{ds}$  = 5.5 V along with high ON-state resistance of 1.02 Ω·mm was reported for GaN device grown by metal-organic chemical vapor deposition [17]. Unfortunately, there are few devices developed for E-mode HEMT's with positive threshold ( $V_7$ ) and high transconductance  $(g_m)$  [13,16]. The device with  $V_{T}$  can secure safe operation of the device while transconductance may provide excellent highfrequency performance [18]. The device aspect ratio  $L_g/T_{CH}$  plays key role in predicting the short-channel effect [19]. It has a direct effect on the DC and RF characteristics. To suppress the short channel effect, a critical aspect ratio has to be held to suppress the short channel effect. To maintain proper electrostatics and retain a relatively high aspect ratio, the gate dielectric and channel thickness need to be scaled along with the gate length [19] to improve high RF performance in nanometer scale gate length. In this paper, we report the device performance of a E-mode HfO<sub>2</sub> -GaN/InN/GaN/In<sub>0.9</sub>Al<sub>0.1</sub>N heterostructure MIS-HEMTs with scaled gate dielectric and InN channel thickness. This work present devices with great potential for RF/power amplifier amplifications by achieving high  $V_{T_{t}} g_{m}$  and high frequency performance  $(f_t / f_{max})$  simultaneously.

Thus, the objective of this study is to investigate the impact of InN channel thickness (t<sub>InN</sub>) and HfO2 as dielectrics on the normally-OFF GaN/InN/GaN/In<sub>0.9</sub>Al<sub>0.1</sub>N heterostructure MIS-HEMTs so as to achieve high  $I_{ds,sat}$ ,  $V_{T_{I}}$ ,  $g_{m_{I}}$ ,  $f_{t}$  and  $f_{max}$  and low intrinsic delay ( $\tau$ ), ON-state resistance ( $R_{ON}$ ) under low voltage bias due to effect of polarization-induced charges at all of the interfaces. Because of the immature state of the InN heterostructures, this type of devices exists only as a theoretical concept [18, 20] and till now no optimization and performance along with the electrical properties of the device were carried out

#### 2. DEVICE ARCHITECTURE

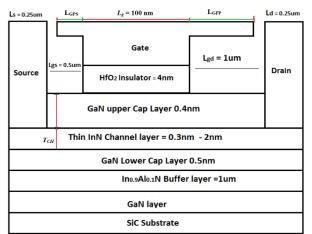

Fig 1 shows the GaN/InN/GaN/In<sub>0.9</sub>Al<sub>0.1</sub>N heterostructure MIS-HEMT used in this research. The bottom layer is an 0.6  $\mu$ m GaN layer, followed by a relaxed 1  $\mu$ m In<sub>0.9</sub>Al<sub>0.1</sub>N back-barrier/ buffer layer. On top of this, a strained 0.6 nm GaN spacer is placed. The role of this spacer is to confine the channel electrons and to screen possible alloy disorder scattering effects coming from the In<sub>0.9</sub>Al<sub>0.1</sub>N buffer [21]. The lattice matched composition of In<sub>0.9</sub>Al<sub>0.1</sub>N layer makes an excellent choice for the buffer to improve channel conductivity in devices [12]. The

active InN channel with  $T_{CH}$  varies from 0.3 – 2 nm, which is strained with an additional strained 0.4 nm GaN spacer on top. This second GaN spacer provides a negative polarization charge at the upper interface of the channel which depletes it from electrons when no gate voltage is applied. Hence, the second spacer that makes the device a normally-OFF transistor. A gate insulator, HfO<sub>2</sub> ( $\kappa \sim 21$ ) with  $t_{ins} = 4$  nm is used below the gate. In addition to the structure, doped regions with  $N_D = 1 \times 10^{20}$  cm<sup>-3</sup> were added around the source and drain in order to assure a good contact with the InN channel. The device has a gate length  $L_q$ = 100 nm, source-gate extension and a gate-drain extension  $L_{sq} = 0.5 \ \mu m$  and  $L_{qd} = 1 \ \mu m$ . The values of the interface polarization charges in the normally-OFF structure are listed in Table 1. Traps were included in the back-barrier and buffer layers to make the substrate semi-insulating.

Table 1: Polarization charge density at each interface

[18]

| [10]                                                |                                                        |

|-----------------------------------------------------|--------------------------------------------------------|

| Parameter                                           | Interface polarization charge <i>N</i> <sub>it</sub>   |

| HfO <sub>2</sub> /GaN interface                     | ~ 10.1× 10 <sup>13</sup> cm <sup>-2</sup>              |

| Upper GaN/InN interface                             | ~ -9.5× 10 <sup>13</sup> cm <sup>-2</sup>              |

| InN/ lower GaN interface                            | ~ 9.5× 10 <sup>13</sup> cm <sup>-2</sup>               |

| GaN/In <sub>0.9</sub> Al <sub>0.1</sub> N interface | $\sim$ -7.8 $\times$ 10 <sup>13</sup> cm <sup>-2</sup> |

#### **3. SIMULATION PROCEDURE**

The simulation of the device was performed using the Sentaurus TCAD K-2015 simulator [22]. The hydrodynamic (HD) transport model that accurately considers the non-equilibrium conditions such as quasi-ballistic transport in the thin regions and velocity-overshoot affect in the depleted regions and the dependence of impact ionization rates on carrier energy distributions was used for device simulation. Several important physical effects such as bandgap narrowing, variable effective mass and doping dependent mobility at the high electric field was also accounted in the simulations [23]. Arora doping dependence mobility model [23] was used to model the effect of mobility, electric field and the carrier temperature. Shockley carrier recombination model, stain and stress polarization model [24, 25] are considered to determine the carrier lifetime and the density in a precise way.

#### 4. RESULTS AND DISCUSSIONS

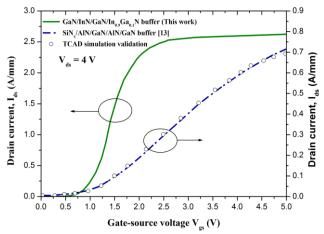

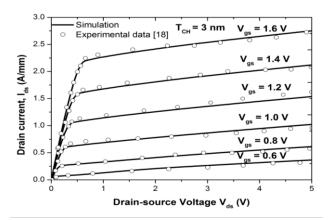

For accurate device simulation, the physical model parameters for transport model are well-matched to the reported measured data [13, 18] as shown in Fig. 2 and Fig. 3. In addition, an optimized device meshing was used to generate robust simulation structures prior to the calibration of physical models. The detailed device meshing and calibration procedure is described elsewhere [26]. The calibrated physical models are used to simulate the device described in Fig.1 and obtain different device characteristics as described below.

Fig. 1 Cross-section of highly confined HfO<sub>2</sub>/GaN/InN/GaN/In<sub>0.9</sub>Al<sub>0.1</sub>N MISHEMT structure used for numerical device simulation. L<sub>g</sub>, L<sub>gs</sub> and L<sub>gd</sub> are the gate length, S/D access region lengths, respectively. T<sub>CH</sub>, a is the channel thickness and gate to channel distance.

Fig. 2. Experimental [13] (solid dotted lines) and simulated (symbols) transfer characteristics for AIN/GaN/AIN MISHEMT after tuning the simulation model to match the experimental curve with our InN channel MISHEMT.

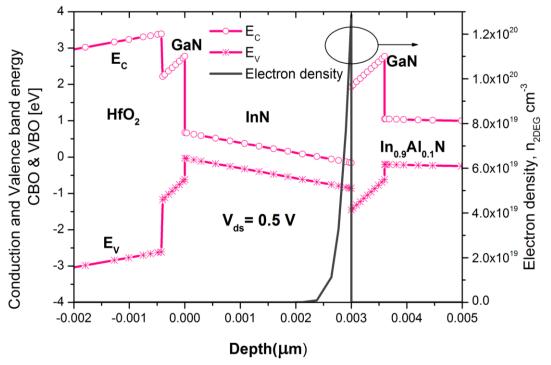

Fig. 4 shows the simulated conduction energy band diagram of the various regions of the device and electron concentration profiles in the channel under the gate for GaN/InN/GaN/In<sub>0.9</sub>Al<sub>0.1</sub>N heterostructure MIS-HEMT for InN channel thickness ( $T_{CH} = 3$  nm). Under the gate, the band-diagram shows that the 2-DEG is completely depleted by the top GaN layer and the device will be normally-OFF. For the normally-OFF structure, a negative interface trap density  $N_{it} \sim -5 \times 10^{13}$  cm<sup>-2</sup> was included at the HfO<sub>2</sub>/GaN interface [18] which lowers the positive polarization charge.

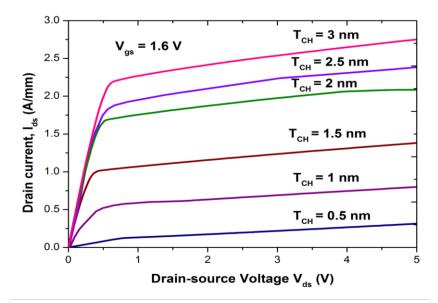

Fig. 5 shows the DC  $I_{ds}$  versus  $V_{ds}$  characteristics of the HfO<sub>2</sub>/GaN/InN/GaN/In<sub>0.9</sub>Al<sub>0.1</sub>N devices described in section II. The saturated drain current ( $I_{ds,sat}$ ) of 2.7, 2.38, 2.09, 1.39, 0.78, 0.315 A/mm is obtained at  $V_{gs}$  = 1.6 V and  $V_{ds}$  = 5 V for devices with  $T_{CH}$  = 3, 2.5, 2, 1.5, 1 and 0.5 nm, respectively. This high value of  $I_{ds,sat}$  is attributed to the superior electron mobility and conductivity in the InN channel.

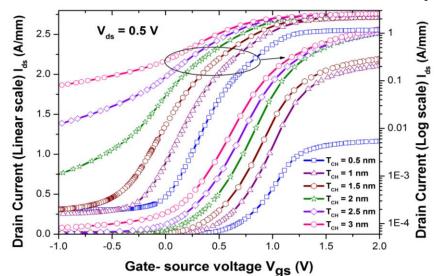

Fig. 6 shows the  $I_{ds}$ - $V_{gs}$  characteristics of a  $L_g = 100$  nm InN channel MISHEMT for  $V_{gs}$  from -1 V to 2 V and  $V_{ds}$ = 0.5 V with  $T_{CH}$  as the third parameter. The simulation data show that for  $T_{CH} = 0.5$ , 1, 1.5, 2, 2.5 and 3 nm the values of  $I_{ds,sat}$  are 1.17, 2.08, 2.18, 2.47, 2.52 and 2.57 A/mm, respectively. It indicates that the current through the channel will become a significant or larger component of the total drive current as the  $V_{gs}$  increases. The increased current capability is due

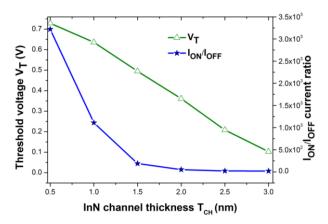

to the presence of high mobility InN channel with high *2DEG* induced close to their interfaces, respectively under a 0.5 V gate bias. From Fig. 8, it has been seen that the  $V_T$  begins to shift positively as the  $T_{CH}$  decreases and device leakage current can be significantly reduced by using high-*k* dielectrics or thin  $T_{CH}$ . The proportion of the amount of the charges in the channel region controlled by the  $V_{gs}$  is increased.  $V_T$  increases almost linearly from 0.102 V for  $T_{CH} = 3$  nm to 0.728 V for  $T_{CH} = 0.5$  nm.

Fig. 3. Experimental [18] and simulated  $I_{ds}$ - $V_{ds}$  curves for InN channel MISHEMT with  $T_{CH} = 3$  nm. The gate voltage was varied from 1.6 V to 0.6 V in step of 0.2 V.

Fig. 4. Simulated conduction energy band diagram and electron density of the device under the gate. The thickness of InN channel is  $T_{CH} = 3$  nm. There is relaxed 1µm In<sub>0.9</sub>Al<sub>0.1</sub>N buffer layer with GaN top and bottom cap layers.

Fig. 5.  $I_{ds}$  as a function of  $V_{ds}$  in InN MISHEMT with various  $T_{CH}$  measured at  $V_{gs} = 1.6 V$ .

Fig. 6. Simulated transfer characteristics of  $I_{ds}$  versus  $V_{gs}$  (both linear and log scale) for various values of  $T_{CH}$  in the InN channel measured at  $V_{ds} = 0.5 V$ .

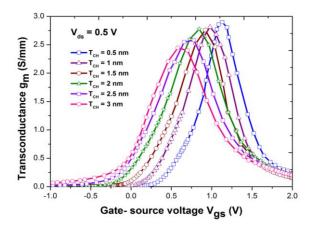

Fig. 7 shows the variation of  $g_m$  as a function of  $V_{gs}$  at  $V_{ds} = 0.5$  V. From Fig. 7, it is found that the values of maximum  $g_m$  for InN channel MISHEMT with  $L_g = 100$  nm is 2.9, 2.81, 2.76, 2.71, 2.58 and 2.44 S/mm for the values of  $T_{CH} = 0.5$ , 1, 1.5, 2, 2.5 and 3 nm, respectively. The device with thicker channel ( $T_{CH}$ ) presents a wider current path and higher 2-DEG density, resulting in a more negative  $V_T$  as well as a decreased peak transconductance [27].

An  $I_{ON}/I_{OFF}$  ratio is a commonly evaluated merit for current technology. This ratio has a significant impact on the static power consumption in low standby power applications and higher values of the  $I_{ON}/I_{OFF}$  ratio are desirable.

Fig. 7. Variation of  $g_m$  as a function of  $V_{gs}$ characteristics for various values of  $T_{CH}$  in InN channel varying from 0.5 nm to 3 nm at  $V_{ds} = 0.5$  V.

The ON-current refers to the drive current in saturation, while OFF-current refers to the total leakage current, which is the sum of subthreshold, gate and junction leakage currents [28] extracted from  $I_{ds}-V_{gs}$  transfer characteristics at  $V_{ds} = 0.5$  V and  $V_{gs} =$ 0 V for  $I_{OFF}$ ,  $V_{gs} = 2$  V for  $I_{ON}$  shown in Fig. 8. It clearly shows that ON current and OFF current is higher for device with higher  $T_{CH}$  due to increased 2DEG along with high gate to channel separation [29]. The threshold voltage dependence on  $T_{CH}$  is shown in Fig. 8. As seen in Fig. 8, the  $V_T$  decreases with increasing  $T_{CH}$  for a given gate length device. As  $T_{CH}$  increases,  $V_{T}$  decreases and becomes more negative due to the increased gate-to-channel distance shown in Fig 8 and achieved a maximum positive  $V_T = 0.828$  V, 0.635 V, 0.494 V, 0.360 V, 0.208 V, 0.102 V for the values of  $T_{CH} = 0.5, 1, 1.5, 2, 2.5$  and 3 nm, respectively. We have also seen that  $V_T$  shifts positive as the  $T_{CH}$  is thinned down. The positive  $V_{7}$  is desired for low-power and enhancement-mode operation.

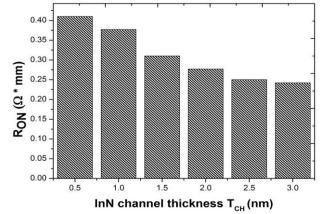

Fig. 9 shows the ON-state resistance ( $R_{ON}$ ) of device with respect to  $T_{CH}$ . For this, the simulation was first performed to obtain the  $I_{ds}$ - $V_{ds}$  characteristic in the DC mode for the values of  $T_{CH} = 0.5$ , 1, 1.5, 2, nm with a step of 0.5 nm. The device  $R_{ON}$  extracted at  $V_{gs} = 1.6$ V and  $V_{ds}$  in the range between 0 and 0.21 V from Fig. 4. The  $R_{ON}$  of the device should be very low to reduce the power consumption in the device switching process.  $R_{ON}$  was found to decrease linearly as  $n_s$ increases [30] and is given by

$$R_{ON} = \frac{L_{gd}}{qn_{\rm s}\mu} \tag{1}$$

where  $L_{gd_r}$  *q*,  $n_s$  and  $\mu$  are the gate to drain access region length, the electron charge, electron sheet carrier density and mobility of the device, respectively. This causes a high device  $R_{ON}$  with decreasing ` $T_{Cr'}$  in the device. We see an increase in  $R_{ON}$  from a value of 0.242, 0.25, 0.277, and 0.41  $\Omega$ ·mm for 2, 1.5, 1, 0.5 nm, respectively. Due to the low channel resistance of the InN channel MISHEMT, the values are low compared to what has been published so far [13,16,17].

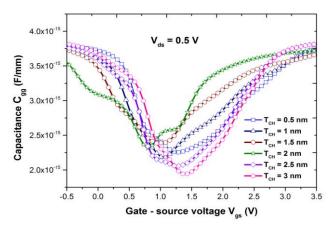

Fig. 10 shows the variation of high frequency (1 MHz) C-V characteristics of the device for various values of  $T_{CH}$  with respect to  $V_{gs}$ . For MISHEMT devices the total gate capacitance ( $C_{gg}$ ) can be given as

$$C_{gg} = Series(C_{ins} + C_{cap}) \parallel C_{gs} \parallel C_{gd}$$

(2)

where

$C_{ins} = \varepsilon_0 \times \varepsilon_{ins} \times \frac{A}{t_{ins}}$

Fig. 8. Variation of  $V_T$  and  $I_{ON}/I_{OFF}$  as a function of various  $T_{CH}$  in InN channel measured at  $V_{ds} = 0.5 V$ .

Fig. 9. Variation of ON-state resistance  $R_{ON}$  as a function of  $T_{CH}$  varying from 0.3 – 2 nm measured from  $I_{ds}$ - $V_{ds}$  characteristics at  $V_{gs} = 1.6$  V.

$C_{ins}$  is the insulator capacitance,  $C_{cap}$  is the depletion layer capacitance comprises of GaN cap top and bottom layers with InN channel,  $\varepsilon_0$  is the vacuum permittivity,  $\varepsilon_{ins}$  is the dielectric constant of high-KHfO<sub>2</sub> dielectric, and A is the capacitor area.  $C_{gs}$  and  $C_{gd}$ are the gate to source and gate to drain capacitances respectively.  $C_{gs}$  and  $C_{gd}$  include the inner ( $C_{if}$ ) and outer ( $C_{of}$ ) fringing capacitances. It is noticed that there is almost negligible effect of  $T_{CH}$  on  $C_{gg}$  before threshold and at strong inversion the capacitance is slightly higher for higher  $T_{CH}$ . This is because in wider channel the carrier confinement is better which gives rise to higher  $C_{gg}$  [31].

The intrinsic delay time ( $\tau$ ) of a transistor is the time taken to charge a constant gate capacitance  $C_{gg}$  to a voltage  $V_{ds}$  at a constant drain current  $I_{OW}$ [32]. The  $\tau$ is a most important figure of merit because it determines the device switching speed depends on mobility and injection velocities of carriers, which are high in case of III-V materials [2] and is given as,

$$\tau = \frac{C_{gg} \times V_{dd}}{I_{ON}}$$

(3)

where  $C_{gg}$  the total gate capacitance,  $V_{dd} = V_{ds}$  is the supply voltage and  $I_{ON}$  is the ON current for various  $T_{CH}$ . Due to higher  $I_{ON}$  in MIS-HEMT devices, the  $\tau$  will be very less and fast device switching can be achieved. Thus, MISHEMTs will have much lower  $C_{gg}$ , leading to the further reduction of delay. Lower values of the  $\tau$  are highly desirable for logic systems and applications requiring high-performance operation [32]. Delay decreases almost linearly from 1.661 Fs for  $T_{CH} = 0.5$  nm to 0.761 Fs for  $T_{CH} = 3$  nm shown in Fig. 11.

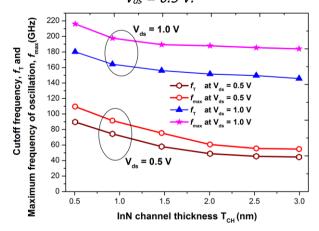

Another important figure of merit for RF application is that cutoff frequency  $f_t$  and the maximum frequency of oscillation  $f_{max}$  which depend on the  $C_{gg}$  and  $g_m$  of a device The  $f_t$  is the frequency when the current gain is unity and is an important measure for high speed digital applications, whereas  $f_{max}$  is the frequency when the power gain is unity and also corresponds with the transit frequency of the maximum available power gain (*MAG*) that is a realistic parameter of the optimization of microwave amplifiers. The  $f_t$  and  $f_{max}$ can be given as [33]

$$F_{t} = \frac{g_{m}}{2\pi C_{gs}\sqrt{1 + 2(C_{gd} / C_{gs})}}$$

$$\approx \frac{g_{m}}{2\pi (C_{gd} / C_{gs})} \approx \frac{g_{m}}{2\pi C_{gg}} - (4)$$

$$F_{max} = \frac{g_{m}}{2\pi C_{gs}\sqrt{4(R_{s} + R_{i} + R_{g})(g_{ds} + g_{m}(C_{gd} / C_{gs}))}}$$

where  $C_{gs}$ ,  $C_{gd}$  and  $C_{gg} = C_{gs} + C_{gd}$  are the gate-tosource, gate-to-drain and total gate capacitances respectively, including fringing and overlap capacitances,  $g_m$  and  $g_{ds}$  are the transconductance and output conductance,  $R_{g_i}$ ,  $R_s$  and  $R_i$  are the gate, source and channel resistance.

Fig. 11 show the variation of  $f_T$  and  $f_{max}$  for different values of  $T_{CH}$  of an  $L_g = 100$  nm device. Fig. 11 clearly exhibit an increase in  $f_T$  and  $f_{max}$  with the reduction of  $T_{CH}$ . This increase in  $f_T$  and  $f_{max}$  is due to the increase in  $g_m$  as  $T_{CH}$  is scaled down. The highest values of  $f_T$  / $f_{max}$  observed are 98 GHz/129 GHz and 200GHz/360 GHz for  $L_g = 100$  nm devices with  $T_B = 0.5$  nm at  $V_{ds} = 0.5$  V and 1.0 V, respectively. The higher  $f_t$  and  $f_{max}$  for the thin channel device ( $T_{CH} = 0.5$  nm) is due to the superior gate-controllability, and hence higher  $g_m$  and lowest parasitic gate capacitances compared to the thick channel ( $T_{CH} = 1$ , 1.5, 2, 2.5, 3 nm) that results from increased gate capacitance [34].

Fig. 10. Gate capacitance  $C_{gg}$  of the 100 nm gate InN channel MISHEMT as a function of various  $T_{CH}$  with  $V_{ds} = 0.5 V.$

Fig. 11. Variation of  $f_t$  and  $f_{max}$  for various  $T_{CH}$  with  $L_g$ = 100 nm at  $V_{ds}$  = 0.5 V and  $V_{ds}$  = 1.0 V.

#### 5. CONCLUSION

The effect of the thickness of InN channel  $T_{CH}$  were studied and analyzed and the successful improvement of device performance of the normally-OFF operation was achieved due to the introduction of HfO<sub>2</sub> as gate dielectrics of the GaN/InN/GaN/In0.9Al0.1N heterostructure. Significant increase in 2DEG, IoN, gm, demonstrates the presence of high current density in the device channel material due to the presence of HfO<sub>2</sub> dielectrics which significantly reduces the current leakage under gate of the device. In addition, incorporation of the strain-free lattice matched In<sub>0.9</sub>Al<sub>0.1</sub>N back-barrier design in E-mode technology provides more flexibility and improvement of E-mode operation of the device. As  $T_{CH}$  becomes thinner, the RF performance of the devices improved and an impressive ft/ fmax peak values of 98 GHz/129 GHz and 200 GHz/360 GHz, respectively, for  $L_q = 100$  nm at  $V_{ds}$ = 0.5 V and 1 V was achieved as against the conventional heterostructure. Furthermore, high frequency performance is possible under high voltage biases and it can be a promising device structure for RF/power amplifier applications.

#### **6. REFERENCES**

- T. Palacios "Beyond the AlGaN/GaN HEMT: new concepts for high-speed transistors" *Phys. Status Solidi* a , vol. 206, Issue 6 , Mar. 2009, pp. 1145–8.

- [2] B.E. Foutz, S.K. O'Leary, M.S. Shur and L.F. Eastman "Transient electron transport in wurtzite GaN, InN, and AIN" J. Appl. Phys., vol. 85, Isssue 11, Feb. 1999, pp. 7727.

- [3] O. Ambacher, B. Foutz, J. Smart, J. R. Shealy, N. G. Weimann, K. Chu, M. Murphy, et.al; "Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures" J. Appl. Phys., vol. 87, Issue 1, Sep. 2000, pp. 334.

- [4] W. Terashima, S.-B. Che, Y. Ishitani, and A. Yoshikawa, "Growth and characterization of AlInN ternary alloys in whole composition range and fabrication on InN/AlInN multiple quantum wells by RF molecular beam epitaxy," *Jpn. J. Appl. Phys.*, vol. 45, no. 20-23, May. 2006, pp. L539–L542.

- [5] E. Dimakis, E. Iliopoulos, M. Kayambaki, K. Tsagaraki, A. Kostopoulos, G. Konstantinidis, and A. Georgakilas, "Growth optimization of electron confining InN/GaN quantum well heterostructure," *J. Electron. Mater.*, vol. 36, no. 4, Apr. 2007, pp. 373–378.

- [6] B. E. Foutz, S. K. O'Leary, M. S. Shur, and L. F. Eastman, "Transient electron transport in wurtzite GaN, InN, and AIN," *J. Appl. Phys.*, vol. 85, no. 11, Jun. 1999, pp. 7727–7734.

- [7] M. Sumiya, K. Yoshimura, T. Ito, K. Ohtsuka, S. Fuke, K. Mizuno, M.Yoshimoto, H. Koinuma, A. Ohtomo, M. Kawasaki, "Growth mode and surface morphology of a GaN film deposited along the N-face polar direction on c-plane sapphire substrate", *J. Appl. Phys*, vol. 88, Apr. 2000, pp. 1158–1165.

- [8] M.H. Wong, Y. Pei, T. Palacios, L. Shen, A. Chakraborty, L.S. McCarthy, S. Keller, S.P. DenBaars, J.S. Speck, U.K. Mishra, "Low nonalloyed ohmic contact resistance to nitride high electron mobility transistors using N-face growth", *Appl. Phys. Lett.*, vol. 91, pp. Issue 23, Dec. 2007, pp. 232103.

- [9] S. Rajan, A. Chini, M.H. Wong, J.S. Speck, U.K . Mishra, "N-polar GaN/AlGaN/GaN high electron

mobility transistors" *J. Appl. Phys.*, vol. 102, Issue. 4, Aug. 2007, pp. 044501.

- [10] M.H. Wong, S. Keller, Nidhi, S. Dasgupta, D. J. Denninghoff, S. Kolluri, et.al., "N-polar GaN epitaxy and high electron mobility transistors" *Semiconductor Science and Technology*, vol. 28, June, 2013, pp. 074009

- [11] Nidhi, S. Dasgupta, J. Lu, J.S. Speck, and U.K. Mishra "Self-aligned N-Polar GaN/InAIN MIS-HEMTs with record extrinsic transconductance of 1105 mS/mm" *IEEE Electron Device Letters*, vol. 33, no. 6, June 2012, pp. 794-796.

- [12] D. Denninghoff, J. Lu, E. Ahmadi, S. Keller and U. K. Mishra "N-polar GaN/InAlN/AlGaN MIS-HEMTs with 1.89 S/mm extrinsic transconductance, 4 A/mm drain current, 204 GHz f<sub>T</sub> and 405 GHz f<sub>max</sub>" *Device Research Conference (DRC)*, Notre Dame, IN, Jun. 2013, pp. 197 – 198.

- [13] U. Singisetti, M.H. Wong, S. Dasgupta, Nidhi, B. Swenson, B.J. Thibeault, J.S. Speck, and U.K. Mishra "Enhancement-mode N-Polar GaN MISFETs with self-aligned source/drain regrowth" *IEEE Electron Device Letters*, vol. 32, no. 2, Feb. 2011, pp. 137-139.

- [14] Nidhi, S. Dasgupta, D.F. Brown, S. Keller, J.S. Speck and U.K. Mishra "N-polar GaN-based highly scaled self-aligned MIS-HEMTs with state-of-the-art  $f_T.L_G$  product of 16.8 GHz-µm" IEEE *International Electron Devices Meeting (IEDM)*, Baltimore, MD, Dec. 2009, pp. 1 3.

- [15] U.K. Mishra "N-Polar deep recess MISHEMTs with record 2.9 W/mm at 94 GHz" *IEEE Electron Device Letters*, vol.37, Issue: 6, May. 2016, pp. 713 – 716.

- [16] K. Shinohara, D.C. Regan, Y. Tang, A.L. Corrion, D. F. Brown, J.C. Wong, J.F. Robinson, et.al., "Scaling of GaN HEMTs and schottky diodes for submillimeter-wave MMIC applications" *IEEE Transactions on Electron Devices*, vol. 60,no. 10, Oct. 2013, pp. 2982-2995.

- [17] X. Zheng, M. Guidry, H. Li, E. Ahmadi, K. Hestroffer, B. Romanczyk, S. Wienecke, S. Keller, and U.K. Mishra"N-polar GaN MIS-HEMTs on sapphire with high combination of power gain cutoff frequency and three-terminal breakdown voltage" *IEEE Electron Device Letters*, vol. 37, Issue: 1, Nov. 2015, pp. 77 – 80.

- [18] J. Kuzmik "Proposal of normally-off InN-channel high-electron mobility transistors" *Semiconductor Science and Technology,* Vol. 29, no. 3, Mar. 2014, pp. 35015-35018(4).

- [19] D.Guerra, R.Akis, F. A. Marino, et al., "Aspect ratio impact on RF and DC performance of stateof-the-art short-channel GaN and InGaAs HEMTs," *IEEE Electron Device Letters*, vol. 31, Issue: 11, Sep. 2010, pp. 1217 – 1219.

- [20] J. Kuzmik "N-Polarity InN/GaN/InAlN highelectron-mobility transistors" *Applied Physics Express,* vol. 5, Apr. 2012, pp. 044101.

- [21] TCAD Sentaurus, *Sdevice User Guide*, ver.G-2015, Synopsys.

- [22] L.K.F. Edwin "Characterization and numerical simulation of gallium nitride-based metal-oxidesemiconductor high electron mobility transistor with High-K gate stack", Master thesis, *Electrical and Computer Engineering, National University of singapore*, Jan. 2012.

- [23] S. Russo, "Gallium nitride-based device simulation and development", *Ph.D. dissertation*, Università di Tor Vergata, 2008.

- [24] O. Ambacher, J.Smart, J. R.Shealy, et al., "Twodimensional electron gases induced by spontaneous and piezoelectric polarization charges in N-and Ga-face AlGaN/GaN heterostructures" J. Appl. Phys., vol. 85, Issue 6, Mar. 1999, pp. 3222.

- [25] S.K. Saha, "Introduction to technology computer aided design," in *Technology Computer Aided Design: Simulation for VLSI MOSFET: C.K. Sarkar (ed.).* CRC Press, Taylor & Francis, Boca Raton, USA, May 2013.

- [26] M.X. Hua, Z.Y. Man, W.X. Hua, Y.T. Ting, P. Lei, C.W. Wei, and L.X. Yu "Breakdown mechanisms

in AlGaN/GaN high electron mobility transistors with different GaN channel thickness values" *Chin. Phys. B*, vol. 24, no. 2, Jan. 2015, pp. 027101.

- [27] H.M. Pardeshi, G. Raj, S. Pati, N. Mohankumar, C.K.Sarkar "Performance assessment of gate material engineered AlInN/GaN underlap DG MOSFET for enhanced carrier transport efficiency" Superlattices and Microstructures, vol.60, Aug. 2013, pp. 10–22.

- [28] P. Å. Nilsson, H. Rodilla, J. Schleeh, N. Wadefalk, J. Grahn "Influence of gate-channel distance in low-noise InP HEMTs" *International Conference on Indium Phosphide and Related Materials (IPRM)*, Kobe, May. 2013, pp. 1 - 2

- [29] A. Raman, S. Dasgupta, S. Rajan, J.S. speck, and U.K. MISHRA "AlGaN channel high electron mobility transistors: device performance and power-switching figure of merit" *Japanese Journal of Applied Physics*, vol. 47, no. 5, May, 2008, pp. 3359–3361.

- [30] M.H. Alam, I. A. Niaz, I. Ahmed, Z.A. Azim, N.Chowdhury and Q.D.M. Khosru "In<sub>x</sub>Ga<sub>1-x</sub>Sb MOSFET: Performance analysis by self consistent CV characterization and direct tunneling gate leakage current" *International Conference on Electro/Information Technology (EIT)*, Indianapolis, IN, May. 2012, pp. 1-6.

- [31] K. Majumdar, P. Majhi, N. Bhat and R. Jammy "HFinFET: A scalable, high performance, low leakage hybrid N-channel FET", *IEEE Transactions on Nanotechnology*, vol. 9, Issue 3, Feb. 2010, pp. 342-344.