### TEMPERATURE DEPENDENT MODELS OF SEMICONDUCTOR DEVICES FOR COMPUTER AIDED ANALYSIS OF ELECTRONIC TRANSDUCERS

ΒY

# TADEUSZ SIDOR DEPARTMENT OF ELECTRICAL ENGINEERING UNIVERSITY OF NIGERIA, NSUKKA. (Received 27th April 1981)

ABSTRACT

The paper presents an investigation of the temperature dependent model of a diode and bipolar transistor built-in to the NAP-2 program and comparison of these models with experimentally measured characteristics of the BA 100 diode and BC 109 transistor. The detail of the modelling technique has been discussed and final results presented.

The Electronic Circuits Analysis NAP-2 Program has been recently installed in the University of Nigeria Computing Centre through the courtesy of Institute of Circuit Theory and Telecommunication, Technical University of Denemark and the great effort of the Computing Centre staff especially Mr. A. McIntosh who adopted the program to the capability of the existing installation.

NOMENCLATURE

base)

$\beta_{\text{F}}$  = forward current gain (common emitted)

#### 1. INTRODUCTION

The temperature dependence of electronic components creates most serious stability problems when electronic transducers are used for accurate measurement purposes. Although some contemporary computer software allows analysis of complex electronic circuits, and basic transducer properties can be investigated during the designing process, future transducer vulnerability to temperature variation can be investigated only if suitable temperature dependent models of the transducer components are built into the software [1].

However because of the very complex nature of the physical processes governing the performance of the semi conductor devices, available models can only approximate their responses. Such models must usually be modified for a given semiconductor which in turn will require some initial investigation of the element characteristics, as the data available in catalogs are neither sufficient nor accurate enough for the modelling purposes.

The NAP-2 built-in models are provided to simulate a semiconductor device performance in the widest range of possible applications: in the cut-off region, in the saturation and active regions, during fast transients and at high frequencies. However for analysis of temperature influence on analog measuring transducers the model accuracy can be limited to the active region only. Also as the transducers usually work at low frequencies, the charge storage effects can be neglected and some of the required model parameters need not be specified. In such a case the default values of unspecified parameters are provided by the program.

The NAP-2 models [2] of semiconductor devices are based on the ideal junction

Diode equation (1)

$$J_{D} = J_{S} \left( \exp\left(\frac{U_{D}}{V_{T}}\right) \right)$$

(1)

where the saturation current  $J_s$  and the  $V_T$  potential are made temperature dependent according to formulae (2) and (3):

$$V_{T} = V_{TO} \frac{T}{298}$$

(2)

(2)

$$J_{S} = J_{SO} \left(\frac{T}{298}\right)^{3} exp\left(\frac{1.1}{V_{TO}} - \frac{1.1}{V_{T}}\right)$$

(3)

where  ${\rm V}_{\rm TO}$  and  $J_{SO}$  values for T=298K.

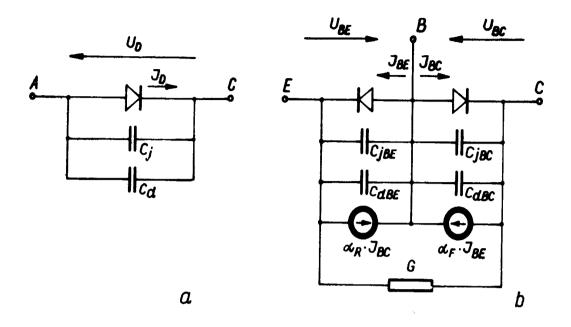

The junction diode is modelled (Fig. la) as a current source described by the equation (1) and two connected in parallel capacitors to represent the charge storage effects. The bipolar junction transistor model (Fig. 1b) is based on the classical Ebers-Moll approach. The additional conductance G between collectors and emitter is added to improve the D.C. model simulation. The bulk resistances of the electrodes are not included in the model descriptions, but can be easily connected externally to the model terminals if necessary. The program offers a facility which enables the model parameters to be entered in or algebraical tabular form, functionally dependent on other circuit parameters, responses or external variables.

As it was mentioned previously, for the low frequency active region models, only certain parameters have to be determined and supplied to the program.

They are as follows:

(i) For the junction diode and baseemitter diode of the transistor  $J_{so}$  saturation current at temperature T = 298 K.  $V_{TO}$  - at temperature T = 298 K.

SIDOR

# 2. MEASUREMENTS

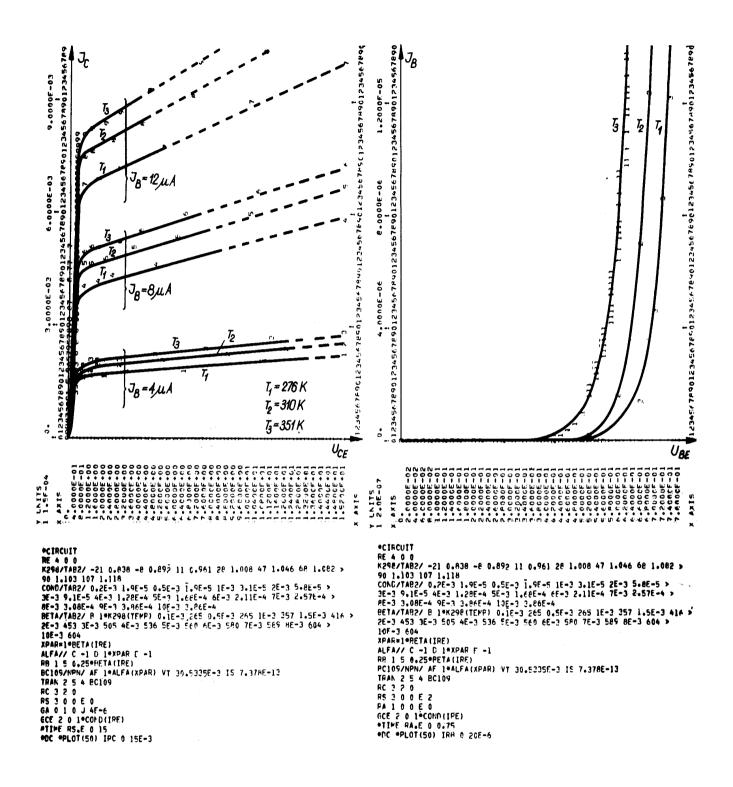

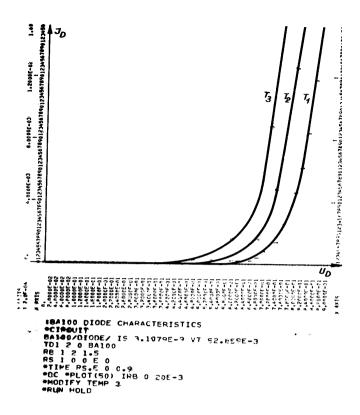

The elements under investigation were immersed in an oil bath in order to provide good heat dissipation from the element enclosure. Using a large vacuum flask the bath temperature was kept practically constant ( $\Delta T < 0.2K$ ) during the series of measurements. The bath temperature was read from a mercury thermometer. Under these conditions the current/voltage characteristics of the diode  $J_D$  (U<sub>D</sub>) and transistor  $J_{C}(U_{CE})$ ,  $J_{B}(U_{BE})$  were taken at 276, 310 and 351 K, using an oscillograph transistor curve tracer and photocamera. It was further assumed that junctions temperature was equal to that of the bath, as the energy lost in the junction during measurements was negligible due to the pulse method employed. The measured characteristics are presented in Figures 5 and 6.

## 3. MODEL PARAMETERS DETERMINATION

The junction diode (and base-emitter diode of the transistor) parameters were determined using basically the technique described by J.C. Bowers and S.R. Sedore [3] with a modification concerning the bulk resistance value finding.

Assuming that for forward currents  $J_D 1$  mA the voltage drop on the diode bulk resistance is negligible and simultaneously the voltage across the diode  $U_D \gg V_T$ , the diode equation (1) can be re-written as (4) which is the equation of straight line in  $In(J_D)$ ,  $U_D$  co-ordinates.

$$\ln (\mathbf{J}_{\mathrm{D}}) = \ln (\mathbf{J}_{\mathrm{S}}) + \frac{1}{V_{\mathrm{T}}} U_D \tag{4}$$

The graph  $In(J_D)$  versus  $U_D$  can be plotted according to the readings taken from the diode characteristic. Using the least square error method the parameters of the equation (4) can be found and the values of  $J_S$  and  $V_T$ determined. For higher forward current values when the voltage drop on the diode resistance is significant, the voltage across the diode can be presented as:

$$U_{\rm D} = J_{\rm D}R_{\rm D} + {}^{\rm V}T \ln\left(\frac{{}^{J}D}{J_{s}}\right)$$

(5)

OR

$$\frac{UD}{VT} - in(J_D) = -in(J_S) + \frac{^RD}{^VT} J_D$$

(6)

Fig. 1: NAP-2 Diode (a) and Bipolar Transistor (b) models

Where  $R_{\mbox{\tiny D}}$  is the diode bulk resistance.

The formula (6) presents again the equation of the straight line in  $(\frac{U_D}{V_T} - \ln(J_D))$ ,  $J_D$  co-ordinates and the similar procedure as described previously can be used to determine the value of  $R_D$

The model parameters have to be specified at the standard temperature of  $T_o$  = 298 K, so the characteristics obtained at T = 310 K has been used as basic reference. The base-emitter diode characteristic  $J_E$  ( $U_{BE}$ ) of the transistor was not measured directly but it can be determined by combining the readings of the two characteristics taken.

It can be noticed that for  $U_{CE} > 2 V$ the  $J_c$  ( $U_{CE}$ ) relationship can be approximated by a straight line (See Fig. 5). Also the input characteristics  $J_B(U_{BE})$  for  $U_{CE} > 2 V$  are practically identical. The following assumptions then seem to be justified. The collector current  $J_c$  can be considered as having two independent additive components produced by two separate effects. One component is controlled only by the emitter current  $J_E$  via the current gain coefficients  $\acute{\alpha}_F$  (dependent

current source in Fig. 1b) and is independent of the  $U_{CE}$  voltage. The second component on the contrary depends on linearity on  $U_{CE}$  voltage and is responsible for collector current rise due to  ${\tt U}_{\tt CE}$  rise. The second component can be easily modelled as conductance G connected across collector and emitter terminals (Fig. lb) therefore it would not affect the emitter diode current. The first component of  $J_{\mbox{\scriptsize C}}$  current (controlled by the base current) can be found in succession from the intersection of the straight line approximating the  $J_{\rm C}\left(U_{\rm CE}\right)$  characteristics for  $U_{\rm CE}$  > 2 V with  $J_c$  axis. The last values added to the suitable base currents give the required values of the emitter diode The corresponding basecurrent. emitter voltages can be found from the transistor input characteristics  $J_{B}(U_{BE})$  for the chosen base current values. The following numerical values have been found:

SIDOR

BA 100 diode

$R_D = 1.5$  ohm.

$J_{so} = 3.108 \times 10^{-9} A$  $V_{TO} = 52.86 \times 10^{-3} V$

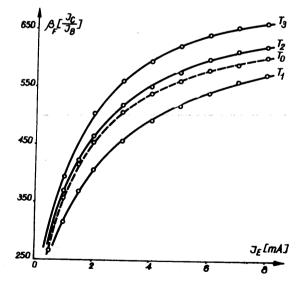

The forward current gain coefficient  $\alpha_{f}$  can be determined using the previously found emitter and base current values. As it might have been expected the  $\alpha_{\rm f}$ value varies considerably with emitter current variation and with temperature. It is usually much easier to find a functional description of  $\beta_{\text{F}}$  value instead (fig.2) because it's temperature dependence can be approximated in the form presented in equation (7) as multiplication by a certain constant temperature dependent К(Т)

$$\beta_{\rm F} = \frac{\alpha_F}{1 - \alpha_F} = K(T) \quad \beta_{\rm O} \quad (J_{\rm E}) \tag{7}$$

Fig.2. Forward current gain of BC 109 transistors as emitter current function.

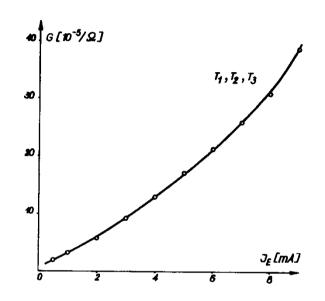

There is no significant variation of the output conductance G with temperature. The G value determined from the slope of the straight lines approximating the linear parts of the  $J_{\rm C}(U_{\rm CE})$

```

BC 109 transistor  J_{So}(BE) = 7.378 \times 10^{-13} \text{ A.} \\ V_{To}(BE) = 30.534 \times 10^{-3} \text{ V} \\ R_{\text{p}} = 0.25 \text{ Ohm.}

```

## Fig. 3: Collector-Emitter conductance of BC 109transistor as emitter current function.

The values of  $\beta_{\circ}(J_{E})$  and  $G(J_{E})$ determined from the Fig. 2 and Fig. 3 respectively are presented in Table 1. The K(T) value determined from Fig. 2 is given in Table 2. The tabulated data cover the G and  $\beta_{\scriptscriptstyle F}$  variation for the limited range of argument (J<sub>E</sub>) variation only. Beyond the specified argument range the NAP-2 program automatically extrapolates the specified data using the slope of the last specified section. As it may cause convergence problem during the а iterative process of calculation, the zero slope of the tabulated curves was artificially introduced at the edges of the specified argument range.

### 4. TEST RUNS.

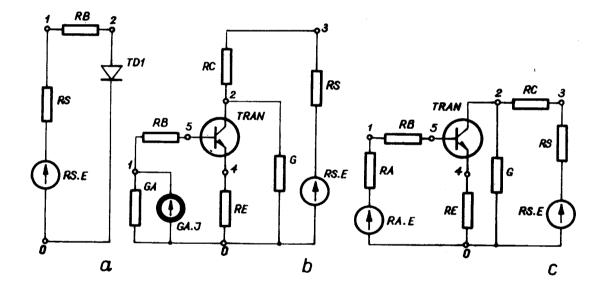

The simple electrical circuits presented in Fig. 4a,b,c have been used to test the models by ordering the computer to TABLE1: FORWARD CURRENT GAIN  $\beta_0$  AND COLLECTIOR-EMITTER CONDUCTANCE G AS EMITTER CRRENNT FUNCTIONS

SIDOR

| $\beta_0 A/A$           | 265 | 265 | 357 | 453 | 505 | 536 | 560 | 580 | 589 | 604 | 604 | 604 |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| G 10 <sup>-5</sup> /ohm | 1.9 | 1.9 | 3.1 | 5.8 | 9.1 | 13  | 17  | 21  | 26  | 31  | 39  | 39  |

| J <sub>E</sub> mA       | 0.2 | 0.5 | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  |

TABLE 2. TEMPERATURE DEPENDENT COEFFICIENT OF FORWARD CURRENT GAIN

| К(Т)             | 0.961 | 1008 | 1.046 | 1.082 | 1.103 |

|------------------|-------|------|-------|-------|-------|

| T <sup>0</sup> C | 11    | 28   | 47    | 68    | 90    |

Fig. 4: Model test circuits for: BA 100 diode characteristics (a), BC 109 output characteristics  $J_{CE}$  (b), BC 109 input characteristics  $JB(U_{BE})$  (c).

print these characteristics which had been used previously for the model parameters determination.

The circuits presented in Fig. 4 contains a number of dummy elements RS = RC = RE = GB = 0. The elements do not affect the circuit performance and were introduced only because their currents and voltages were needed as references in the program. The most important is the  $J_E$  current flowing through RE resistor and denoted IRE in the program, as it was made to control the  $\beta_o$  and G values. The RB resistor

represents the base bulk resistance and its value equals to  $(\beta_{\rm F}-1)$  RE. The conductance G was artificially connected outside the basic built-in transistor model, as its value rises with  $\boldsymbol{J}_{\scriptscriptstyle E}$  current which some-time causes a convergence problem. The print-out of the program listings and computer model characteristics together with the measured characteristics are presented in the fig. 5 for the BC 109 transistor and in the fig.6 for the BA 100 diode.

Fig.5. computed model characteristics, print-out of the programs and measured characteristics of BC 109 transistor. Output characteritics (a), Input characteristics(b).

SIDOR

Fig.6.Computed model characteristics, print-out of the program and measured characteristics of BA 100 diode.

#### 5. CONCLUSION

As it can be seen from Fig. 5 and Fig. 6 the computed characteristics of chosen semiconductor elements fit well to the measured very Characteristics. fact the In differences never exceed 3% of the measured values and can be considered negligible for practical purposes, as the parameter spread among semiconductor elements even from the same batch is usually much greater. The modelling technique used seems to

transducer adequate to the be analysis requirements as the resultant models describe properly the influence of temperature and electrical inputs on the element characteristics. It makes fully possible to use such models for complex electronic transducer circuit analysis using the NAP-2 program, especially when temperature influence on the transducer performance has to be investigated. It should be stressed that the described models are fully applicable in the active region only, for 2 V <  $U_{\rm CE}$  < 10 V and 0.1 mA <  $J_{\rm C}$  <10 mA and at low frequencies, as the effects beyond this range were neglected during the modeling process.

#### REFERENCES

- K. Geher, Theory of Network Tolerances, Akademiai Kiado Budapest, Hungary 1971.

- Thomas Rubner-Peterson, NAP-2 a Nonlinear Analysis Program for electronic circuits, version 2,Users Manual 16/5-73, Institute of Circuit Theory and Telecommunication Technical University of Denemark.

- 3. James C. Bowers, Stephan R. Sedore, SCEPTRE A Computer Program For Circuit and System Analysis, prentice-Hall Inc. Englewood. Cliffs, New Jersey, 1971.